Hi, TI team.

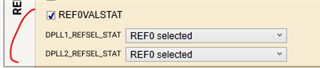

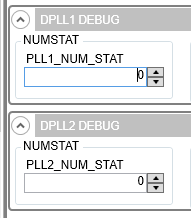

I had a few questions about phase locked. The 4 outputs of DPLL2 have a fixed phase with input clock (REF0) but the other 4 outputs from DPLL1 do not. Until now, we asserted four status (PLL1 Lock Detected, PLL2 Lock Detected, DPLL1 Loss of Lock and DPLL2 Loss of Lock) are all normal.

I tried to change DPLL phase lock threshold (with register R359 and R360). But it still does not solve the problem.

The questions are:

1.How can I make the phase of DPLL1 locked?

2.Why are the two DPLLs different?

Attached is my configuration file of TICs pro. Thank you and looking forward to your reply.