Hi Timothy T

We have a custom board with LMK04828 and RFSoC.

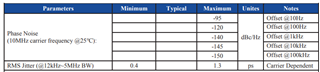

We are observing Phase noise of LMK output to be very less around -95 to 100 dBc/Hz at 1K to 100KHz offset

Due to this, RF DAC Outputs also have same Phase noise.

Below attached schematic of LMK Section:

We have tried changing Loop filter CP1 values of C622 to680nF, C623 to100nF and R402 to 39K. Still the same result of phase noise.

Please suggest us how we can improve the phase noise.

Below attached Phase noise for reference.

Phase noise of VCXO 100MHz (Y10)

Phase noise of LMK Output (DCLKOUT6)- 256MHz

Phase noise of DAC Output (440MHz)