Other Parts Discussed in Thread: LMK04828

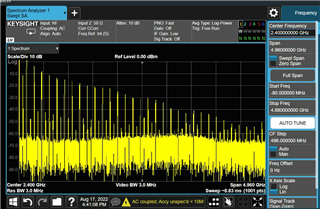

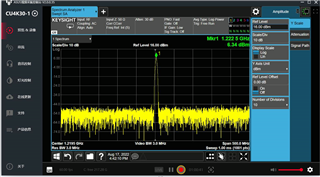

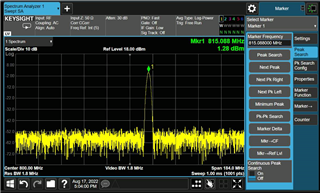

After removing the C4, R3_AB1 and R18 devices and connecting R1 to ensure that the clock of the board is completely powered off, I connected OSCin* and CLKin1* to two 100M 3DBM signals output by the same signal source (which have been calibrated by the spectrum analyzer) and conducted online configuration through TICS PRO. The target requires the output of 2.4g frequency points, but observing the spectrum analyzer, the frequency point of VCO0 cannot be obtained without any frequency. After frequency division, the output clock will be offset. If 1200M is configured, 1222M will be obtained, and if 800M is configured, 815M will be obtained. Do we need to remove the clock CVHD-950-122.88? Or is there another way of thinking about it? DCLKout0 of the output terminal.