Hi all,

We referred to the LMX2594 datasheet but are not fully clear on the SYNC category and it’s a necessity to get a stable phase.

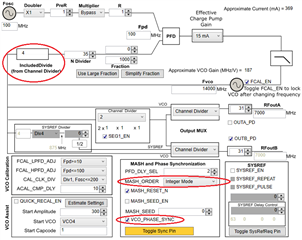

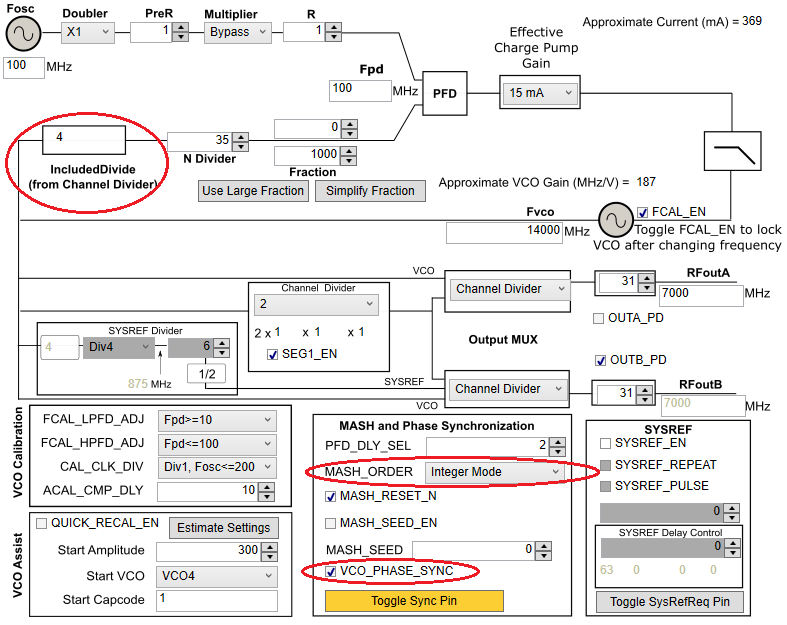

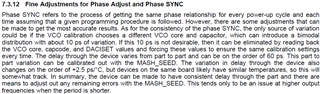

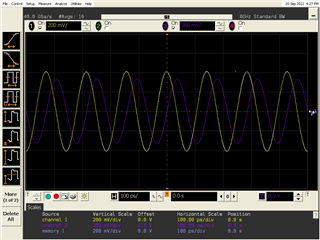

Our Post-R Divider = 1, Channel Divider = 2, reference clock is 100MHz and Fout = 7GHz. As per the flow chart to determine the SYNC category in the LMX2594 datasheet, it points to Category 1 where no software/pin SYNC pulse is required. However, we observe unstable phases over time though we are setting VCO_PHASE_SYNC = 1, INPIN_IGNORE = 1. Do we need to toggle VCO_PHASE_SYNC from 0 to 1 keeping FCAL_EN = 1 additionally?

Kindly suggest on identifying the SYNC category and configuring correct registers.

Thanks

Atul