Hey team,

Quick question on INPIN_IGNORE.. if the following sequence is done, the device will synchronize properly, right? This seems to be how the datasheet explains it as INPIN is only valid while SYNC is 1.

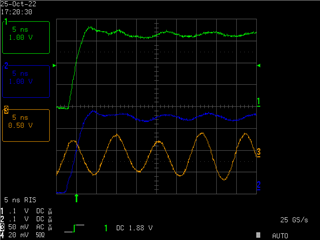

- We set VCO_PHASE_SYNC=1 and INPIN_IGNORE=0 to enable phase synchronization.

- We drive the sync input with a periodic signal. So sync is triggered continuously.

- After a while, we set INPIN_IGNORE=1 right before a rising edge of the periodic sync input, to ensure that no further pulses will have an effect.

Thanks,

Cam