Part Number: LMK04828-EP

Hi,

We have developed some PCBs with the LMK04828SNKDTEP. What we observe is some of them lock to an external reference (PLL1) almost automatically, some of them take some more time to lock and some of them don't lock at all.

Some inputs that could be helpful to know:

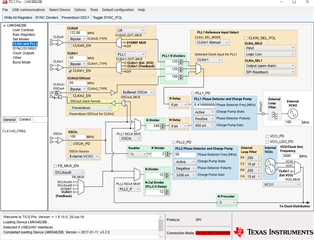

This is how we configured our LMK

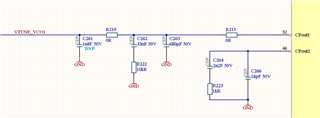

The external loop filters can be found below

- An additional behavior we have notice is that we observe some "ageing", i.e, we have some samples we use to lock automatically, then took some time to lock, then they stop locking again.

- We have notice that some of the samples lock if we relax the digital locking condition, i.e window of 43 ns with 8192 counter to a counter with 768.

We have measured the temperature and we don't seem to excess the maximum ratings of the device.

Could you please orient us about what we could have go wrong?

Best regards,

Manuel.