Other Parts Discussed in Thread: , LMK00804, LMK1C1102, LMK1C1104

Hi,

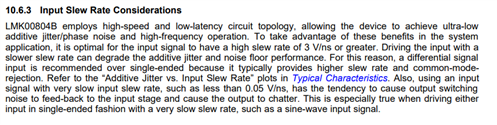

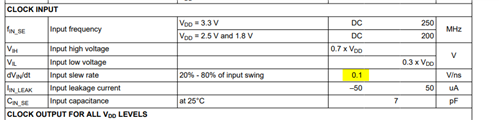

Or the basic question is: Please note the required Input driver (or even parts) for LMK00804B as 3V/ns otherwise chatter O:(

More about my use:

I use the LMK00804B as clock distribution driving from an 0.5/ns OXCO 10Mhz as digital AHC 3.3V output.

The project is a research on Jitter measurements in a different way as seen today.

I see this Chatter clearly at the output using the LeCroy WM8600A at 200G/s, as low frequency flutter or low freq. Jitter.

I like the LMK00804B, as has a synchronized output stop / start. Only missing not having to inputs for clock switching.

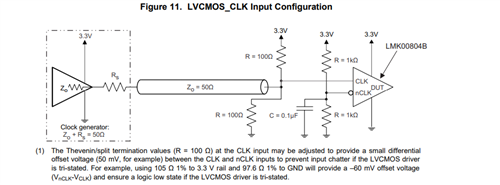

Also, did not found any benefits in terms of performance benefit if I would build or connect to the symmetric input buffer.

There is also a new LMK00804B-Q1 as different food print. I means as this chip is equal or any different?

Best regards

Hanspeter