Hi,

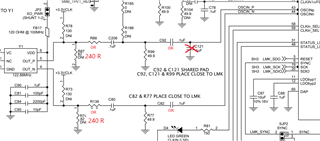

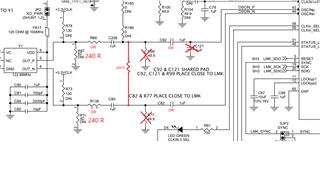

We are using DAC3XJ8XEVM EVAL Board which default comes with 122.28MHz LVCMOS to OSCIN.

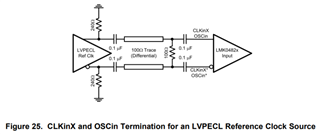

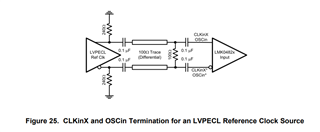

We are changing the Y1 to 100MHz LVPECL https://www.crystek.com/crystal/spec-sheets/vcxo/CVPD-922.pdf and followed LVPECL Input circuit to OSC IN Input

But the PLL2 is not locking.

With external Input to J17 CLKIN1 PLL1 is locking but PLL2 is not locking

Anything we are missing..?