Hi,

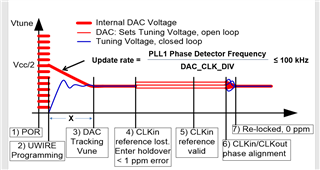

I am facing issue with PLL1 locking to a reference input which runs negative in ppm to the current holdover clock (or the previous reference input).

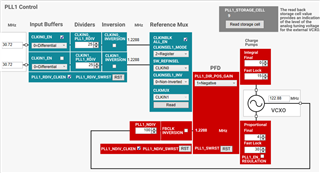

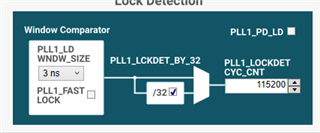

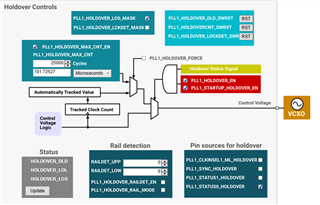

Image below shows my input and PLL1 and holover configuration, I am using holdover feature where PLL1_HOLDOVER_LCKDET_MASK is unticked to make sure that the device switch to holdover upon PLL loss lo lock.

The device is comfortably entering in to the holdover up-on an LOS or ppm changes triggered from tester.

For any positive ppm changes at the input clock, the PLL1 is able to lock once I set the PLL1_HOLDOVER_LOCKDET_SWRST to initiate the reset from holdover.

But for many a times for any negative ppm change from the tester, PLL1 is unable to lock to the reference even after the PLL1_HOLDOVER_LOCKDET_SWRST is set even after getting the input clock to a stable (a negative ppm change)

As shown in the image below, I have enabled the PLL1_LOL_NORESET.

The PLL1_RC_CLK_EN flag is Disabled. Can you please let me know what is this feature about?

Kindly review and suggest on what could be going wrong in my configuration or system.

Thanks,

Vinod