Hi!!

I am evaluating the performance of our internal PLL.

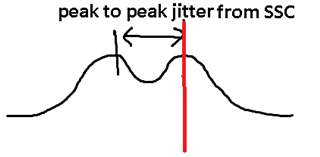

We are expected to measure the “additional” Jitter introduced by the spread-spectrum clock.

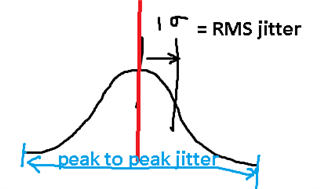

Generally, a clock with Jitter is: Fundamental_Frequency + Error.

The following waveform shows a ~1.15GHz clock with 100KHz SSC modulation – you can see that the waveform is frequency modulated and it moves across time – this periodic movement is what I would call as Desired Jitter.

With SSC modulation enabled, the PLL is going to induce an error, i.e., the modulated clock = Fundamental_Frequency +/- Modulation_shift (or periodic movement or Desired Jitter) + Error.

We intend to measure this Error.

This activity is to quantify how our PLL performs when it is enabled with SSC.

Awaiting guidance on this.

Best Regards,

Kumaran Anand B