Hi there,

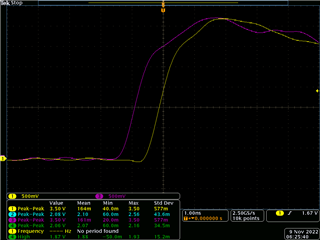

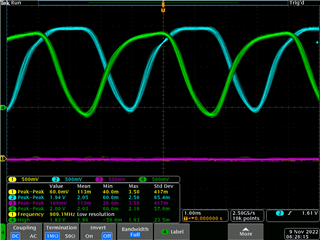

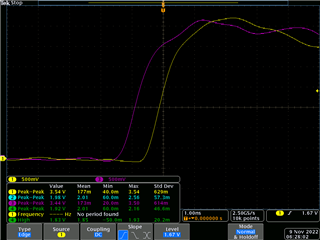

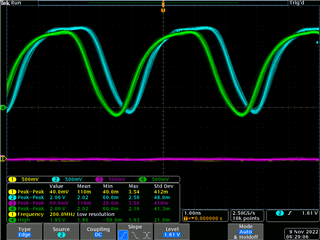

I have two LMK04828 to be synchronized. However, I get ±1 VCO cycle error for LMKs' output device clock (DCLKout2) aligning after power-cycle.

I didn't use any PLL on LMK04828. Therefore, only divider reset was involved in the synchronization.

The external 1GHz clock is distributed to CLKin1 port on LMKs with the same path length.

The SYNC was performed by toggling SYNC pins on LMKs simultaneously with identical length.

For SYNC operation, I used normal SYNC mode. For SYSREF operation, I used SYSREF pulser mode.

The following is my register config:

(0x0000,0x90)

(0x0000,0x10)

(0x0000,0x10)

(0x0100,0x61)

(0x0101,0x22)

(0x0103,0x02)

(0x0104,0x20)

(0x0106,0xf0)

(0x0107,0x55)

(0x0108,0x64)

(0x0109,0x22)

(0x010b,0x07)

(0x010c,0x20)

(0x010e,0x80)

(0x010f,0x11)

(0x0110,0x61)

(0x0111,0x22)

(0x0113,0x02)

(0x0114,0x20)

(0x0116,0xf0)

(0x0117,0x57)

(0x0118,0x61)

(0x0119,0x22)

(0x011b,0x02)

(0x011c,0x20)

(0x011e,0xf0)

(0x011f,0x57)

(0x0120,0x62)

(0x0121,0x22)

(0x0123,0x05)

(0x0124,0x20)

(0x0126,0xb0)

(0x0127,0x11)

(0x0128,0x68)

(0x0129,0x22)

(0x012c,0x20)

(0x012e,0xf7)

(0x012f,0x01)

(0x0130,0x61)

(0x0133,0x02)

(0x0134,0x20)

(0x0136,0xf7)

(0x0138,0x40)

(0x0139,0x00)

(0x013a,0x01)

(0x013b,0x00)

(0x013c,0x00)

(0x013d,0x08)

(0x013e,0x02)

(0x0140,0xf0)

(0x0143,0x91)

(0x0143,0x91)

(0x0143,0x11)

(0x0144,0x49)

(0x0145,0x7f)

(0x0146,0x00)

(0x0147,0x10)

(0x0148,0x33)

(0x0149,0x40)

(0x014a,0x02)

(0x014b,0x05)

(0x014c,0xff)

(0x0150,0x00)

(0x0156,0x78)

(0x015f,0x0b)

(0x0161,0x01)

(0x0162,0x44)

(0x016e,0x13)

(0x0171,0xaa)

(0x0172,0x02)

(0x0173,0x60)

(0x017c,0x15)

(0x017d,0x33)

(0x1ffd,0x00)

(0x1ffe,0x00)

(0x1fff,0x53)

Toggle SYNC pins on LMKs simultaneously

(0x0144,0xff)

(0x0143,0x12)

(0x0139,0x02)

My question is that whether ±1 VCO cycle error is expected to happen for LMKs' output device clock aligning? Did I miss anything to synchronize the LMKs? Shall I use zero-delay mode to get rid of the VCO cycle error?

Thanks and best,

Yilun