Other Parts Discussed in Thread: LMK00304

Hi,

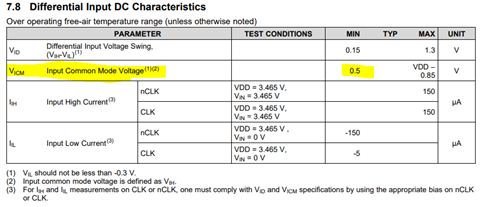

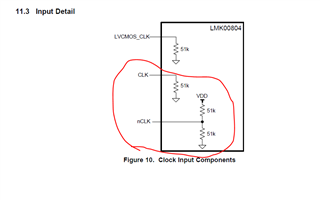

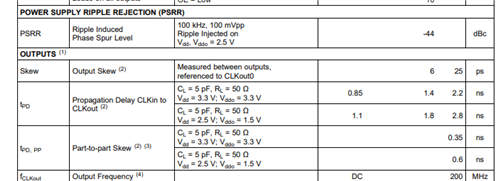

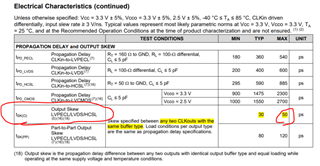

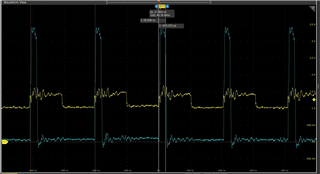

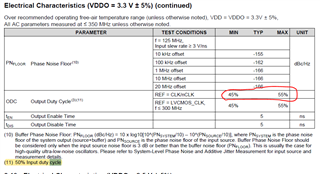

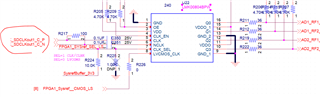

The input clock of LMK00804B is 4.8828125MHz LVDS clock with AC-couple, and it have ~50% dute cycle(yellow curve in below figure). But the dute cycle of output clock is not in the range of 45%~55%(blue curve) as mentioned in datasheet as below figure shown. why?

Thanks in advance!!!

Best regards!

Jason