Hi team

1. In the datasheet 10.2.2 Detailed Design Procedure, it says

"Determine the average output load seen by all clock outputs Y[3:0]."

for the first step of optimizing the propagation delay of the PLL.

In the case below,

1Y0=1Y1=4pF、1Y2=1Y3=0pF(not connected)

Is the average output load 4 pF or (4pF+4pF+0pF+0pF)/4=2pF?

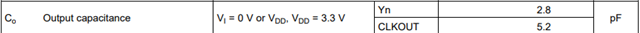

2. For the average output load calculation, should we include the output capacitance of the device shown in the datasheet?

Regards,

Ohashi