Other Parts Discussed in Thread: LMK5B33414

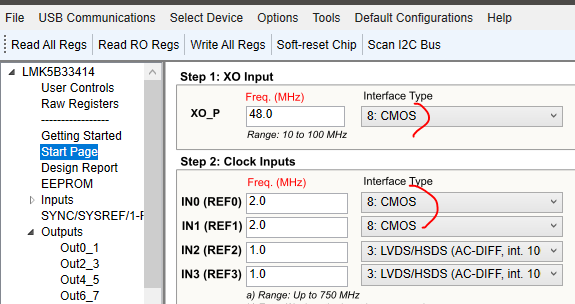

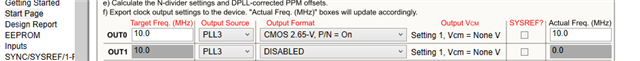

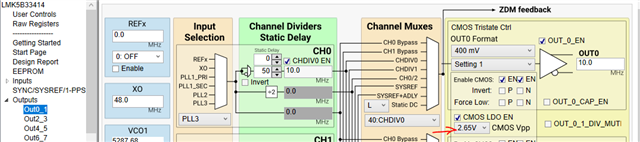

I need a reference clock of 10 MHz with the lowest possible jitter for a laboratory and I don't have a lot of experience in programming clock products.

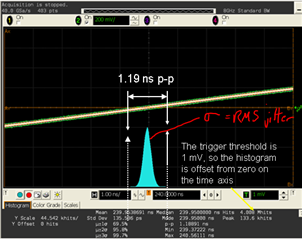

As a reference I use the Ublox ZED-F9T. My measurements has shown that frequencies based on integer dividers of 128MHz have the lowest jitter (+/- 0.4 ns).

All other frequencies show a jitter of +/- 5 ns and correspond to the data sheet.

The Ublox ZED-F9T can be set to frequencies <25 MHz. The duty cycle can be set to e.g. 50%.

It would be very helpful for me at the moment, if I could get a TICS-Pro configuration file.

I use the LMK5B33414EVM board. The clock from the ZED-F9T is fed in at IN0_P and has an amplitude of 3.3 V.

It would be very helpful for me at the moment to have a configuration file with 1PPS and a configuration file for a fixed frequency (e.g. 1 MHz) fed in at IN0_P.

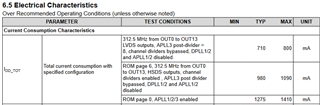

I have another question about the heat generated by the LMK5B33414 chip. I have successfully generated some frequencies at OUT1 and OUT 2 for a first function test. I configured these outputs as "CMOS 2.65-V, P/N = On". I deactivated all other outputs. The chip hardly heats up with this configuration. The data sheet (SNAS835 – SEPTEMBER 2022 Page 23) describes that in the HCSL output configuration, the outputs must each be terminated with 50 ohms. I followed that and also configure another output to HCSL 750mV. As soon as I write this configuration into the board, the chip gets very hot. I felt the temperature with my finger and have the impression that a heat sink is necessary. Due to the heat development, I preferred not to configure any additional output in order not to damage the chip. I saw that there are shunt resistors that can be switched on the board to determine the current consumption. I haven't done any further measurements yet. Is this heat development normal, or have I done something wrong ?

I would like to thank you in advance for the effort.

Yours

Stefan