Hi,

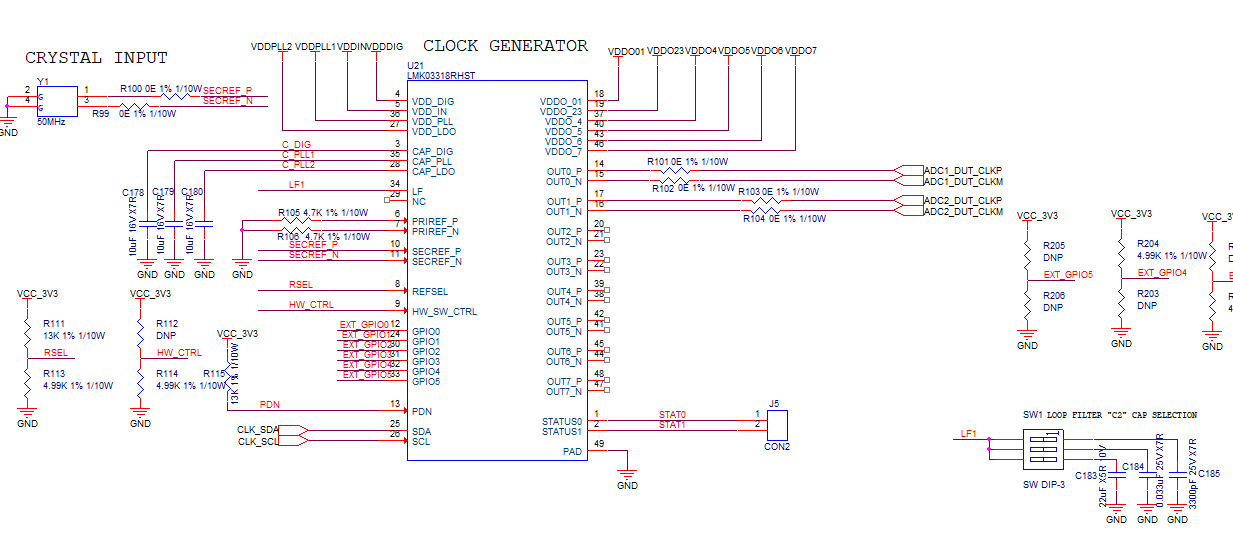

Below is my applicaiton schematic for LMK03318, the device is programmed for the LVPECL output of 500MHz

I am using register programming straight away to see the clock output

I have a found a minor glitch, i am not sure why its occuring

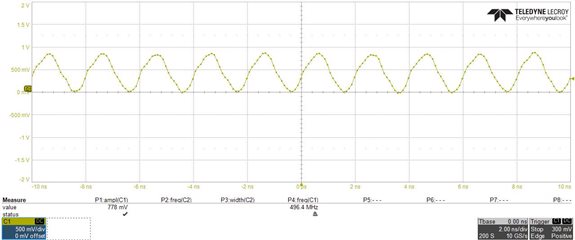

below are my output waveforms, output swing through a diff probe is below for a programmed 500MHz clock output

but when i increase timescale, i see the clock source is stagnant for 1ms for every 100ms, why this might be happening ? below is waveform

i did below experiment

Step 1: clock is out after programming

Step 2 : OFF all DIP switches

Step 3 : I can observe the Clock being similar

Step 4 : i have a again Enabled 3300pF to LF1 which made the clock to be stable with out any restart every 100ms

I could not understand why this process made the clock stable , why should i play with the LF1 cap at run time ?

i am also attaching the configuration file