Other Parts Discussed in Thread: LMK61E2,

Hi team,

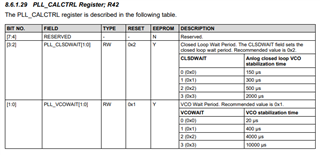

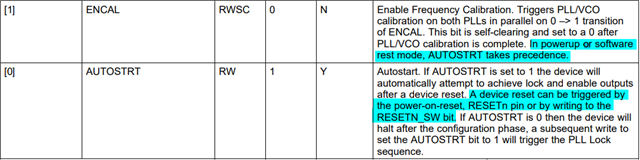

What is the function of these register bits (SWR2PLL, AUTOSTART and ENCAL)? How to use them?

Does both the AUTOSTART bit and the ENCAL bit have a function to trigger PLL Lock?

For ENCAL bit, what is software rest mode?

Device does not have RESETn pin and RESETN_SW bit, how do user use the AUTOSTRT bit?

Could you lease leave your comments? Thanks in advance.

Best Regards,

Amy Luo