Other Parts Discussed in Thread: LMX2594, LMK61E2

Hi,

In my design, I use one LMX04828B to provide reference clock and Sync signal to four LMK2594. Sync signal are used for aligning SYSREF clock(4.8828125MHz) form RFoutB of four LMK2594.

But I found that sometimes the four SYSREF clocks could be aligned completely after power on, and sometimes not. Could you please help me check this issue? May be some mistake in the procedure?

After power on, the sequence of clock configuration is: LMK04828 1st configuration(basic configuration) -> LMK2594 configuration -> LMK04828 2st configuration(generate Sync to LMX2594)

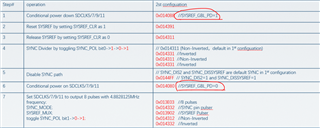

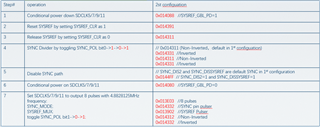

LMK04828 1st configuration, and SDCLK5/7/9/11 are ready for 4 SYNC signals; DCLK2 and SDCLK3 are provided to FPGA

LMK61E2_100M_SinglePLL_PD 25M_LMX2594_4 SYNC.tcs

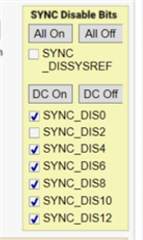

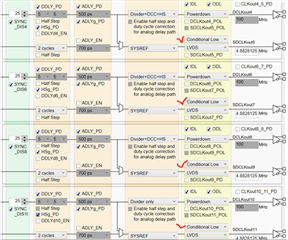

LMK04828 2st configuration: total 17 register operation marked with red is to make SDCLK5/7/9/11 output 8 continuous pulse with 4.8828125Mhz as SYNC signal for 4 LMX2594

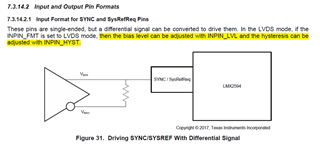

The INPIN_LVL of LMX2594 is set as Vin because default value with Vin/4 don't take effect

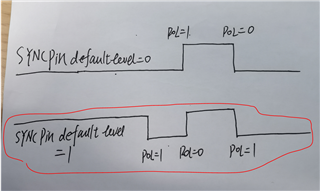

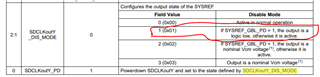

output format of SDCLK5/7/9/11 is LVDS, so SYNC format of LMX2594 is set according to below figure. The C215 and C216 have been replaced with 0 ohm resistors

Thanks in advance!!!

Best regards!

Jason