Part Number: LMK1D1204

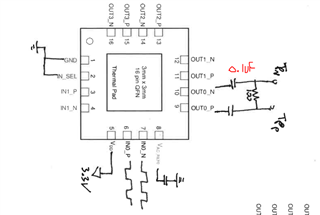

I am testing the LMK1D1204 LVDS clock buffer on a breadboard to determine if it will work with a design. I am using a VDD of 3.3V and inputting a differential clock signal from 0-2V yet the output is at a 0.5V steady state before the 0.1uF caps and 0V after the caps. Below is our configuration we are trying. At this moment we are not concerned about noise as this is just a simple “will it work” test. Is it possible that the floating inputs (IN1_P and IN1_N) are activating the fail-safe?