Other Parts Discussed in Thread: LMX2594

Hi Team,

Good day. I am posting this inquiry on behalf of the customer.

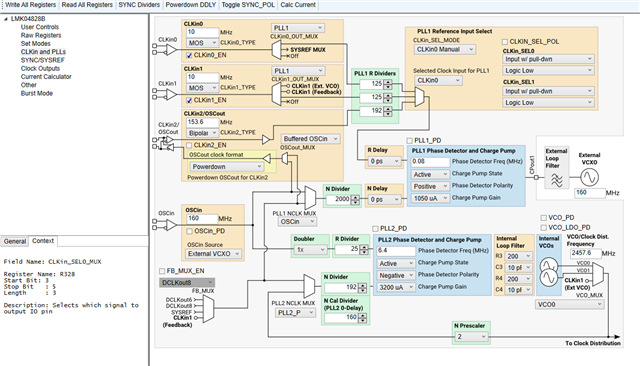

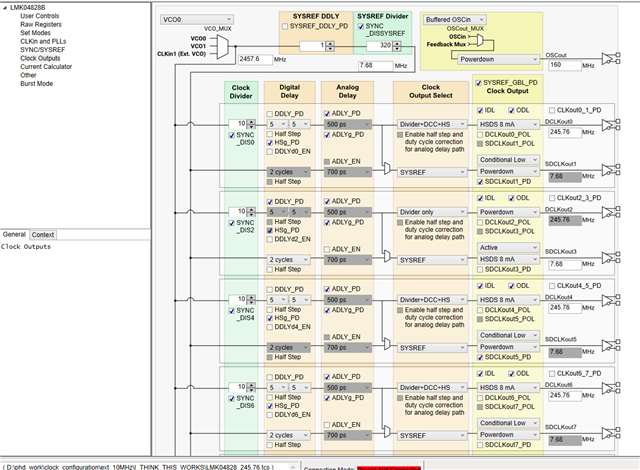

"I am working on RFSoC4x2 (Gen3 XCZU48DR) with PYNQ version 2.7.0 and vivado 2020.2

My primary requirement is to configure LMK04828 chip on board to take external 10MHz ref clock input and produce 245.76MHz to feed to LMX2594 chip which, in turn, is generating 409.6MHz. I did generate .tcs (and .txt) configuration file for the same and added the corresponding .txt file (i.e. LMK04828_245.76.txt) in xrfclk package in JupyterNotebook environment (path: /usr/local/share/pynq_venv/lib/python3.8/site-packages/xrfclk). Also, I am setting these clocks using command

xrfclk.set_ref_clks(lmk_freq=245.76,lmx_freq=409.6)

Now the problem is- My design is working even when I am not feeding the external clock to the board which means it’s definitely taking driving_clock from another input pin and I can’t figure out which one or there's something which I am missing here.

Could you please guide and help me resolve this issue?

Attached is my config file (.tcs) and hex register (.txt) file for reference and also some snaps which might be helpful for you to understand the issue more clearly. "

R0 (INIT) 0x000090

R0 0x000010

R2 0x000200

R3 0x000306

R4 0x0004D0

R5 0x00055B

R6 0x000600

R12 0x000C51

R13 0x000D04

R256 0x01006A

R257 0x010155

R258 0x010255

R259 0x010301

R260 0x010422

R261 0x010500

R262 0x010673

R263 0x010703

R264 0x01086A

R265 0x010955

R266 0x010A55

R267 0x010B00

R268 0x010C22

R269 0x010D00

R270 0x010EF0

R271 0x010F30

R272 0x01106A

R273 0x011155

R274 0x011255

R275 0x011301

R276 0x011422

R277 0x011500

R278 0x011673

R279 0x011703

R280 0x01186A

R281 0x011955

R282 0x011A55

R283 0x011B01

R284 0x011C22

R285 0x011D00

R286 0x011E72

R287 0x011F03

R288 0x012074

R289 0x012155

R290 0x012255

R291 0x012301

R292 0x012422

R293 0x012500

R294 0x012670

R295 0x012733

R296 0x01286A

R297 0x012955

R298 0x012A55

R299 0x012B00

R300 0x012C22

R301 0x012D00

R302 0x012EF0

R303 0x012F30

R304 0x01306A

R305 0x013155

R306 0x013255

R307 0x013301

R308 0x013422

R309 0x013500

R310 0x013673

R311 0x013703

R312 0x013800

R313 0x013903

R314 0x013A01

R315 0x013B40

R316 0x013C00

R317 0x013D01

R318 0x013E03

R319 0x013F02

R320 0x014009

R321 0x014100

R322 0x014200

R323 0x014331

R324 0x0144FF

R325 0x01457F

R326 0x01461B

R327 0x01470A

R328 0x014802

R329 0x014942

R330 0x014A06

R331 0x014B26

R332 0x014C00

R333 0x014D00

R334 0x014EC0

R335 0x014F7F

R336 0x015011

R337 0x015102

R338 0x015200

R339 0x015300

R340 0x01547D

R341 0x015500

R342 0x01567D

R343 0x015700

R344 0x0158C0

R345 0x015907

R346 0x015AD0

R347 0x015BDA

R348 0x015C20

R349 0x015D00

R350 0x015E00

R351 0x015F0B

R352 0x016000

R353 0x016119

R354 0x016244

R355 0x016300

R356 0x016400

R357 0x0165A0

R369 0x0171AA

R370 0x017202

R380 0x017C15

R381 0x017D33

R358 0x016600

R359 0x016700

R360 0x0168C0

R361 0x016959

R362 0x016A20

R363 0x016B00

R364 0x016C00

R365 0x016D00

R366 0x016E13

R371 0x017300

R386 0x018200

R387 0x018300

R388 0x018400

R389 0x018500

R392 0x018800

R393 0x018900

R394 0x018A00

R395 0x018B00

R8189 0x1FFD00

R8190 0x1FFE00

R8191 0x1FFF53

Please help to advise. Thank you for extending your support.

Kind regards,

Marvin