Other Parts Discussed in Thread: CDCM6208,

Hi TI Support,

I am having a problem with the CDCM6208V2. Can you help me? I am almost certain it has to do with the external loop filter on the chip. I know this because of all the debugging and testing I've done, also, this device worked well for me on Version 1 of my board where I had a slightly different ELF. I am seeing noise up at 7.5 GHz created and dumped all over the board, but as I get my ELF closer to that of V1, I saw this start to disappear and the chip not be noisy.

Here are the values I am programming into the registers (getting about 780 ish kHz out of the fractional divider outputs)

reg_config_t cdcm6208_reg_def[21] = {

{0x0000, 0x01B8, 0}, // 0 // 01B8

{0x0001, 0x0000, 0}, // 1

{0x0002, 0x0013, 0}, // 2

{0x0003, 0x08FA, 0}, // 3

{0x0004, 0x30E3, 0}, // 4

{0x0005, 0x0001, 0}, // 5

{0x0006, 0x0000, 0}, // 6

{0x0007, 0x0001, 0}, // 7

{0x0008, 0x0000, 0}, // 8

{0x0009, 0x06D3, 0}, // 9 0x06D3 for LVCMOS / 603 for lvds // 3

{0x000A, 0x0D40, 0}, // 10

{0x000B, 0x1352, 0}, // 11

{0x000C, 0x0619, 0}, // 12 HCSL // B

{0x000D, 0x0D40, 0}, // 13

{0x000E, 0x1439, 0}, // 14

{0x000F, 0x06D3, 0}, // 15 LVCMOS // 3

{0x0010, 0x0D40, 0}, // 16

{0x0011, 0x1352, 0}, // 17

{0x0012, 0x06D1, 0}, // 18 LVCMOS // 3

{0x0013, 0x0D40, 0}, // 19

{0x0014, 0x1352, 1} // 20

};

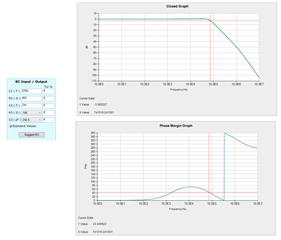

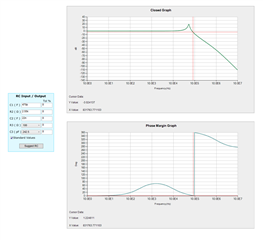

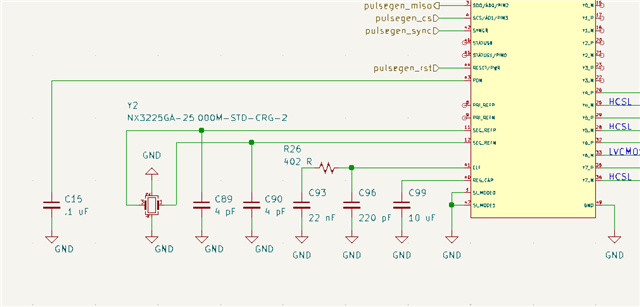

In the attached ELF and Clock.png picture, you can see the ELF values my circuit is using and the 25.0000MHz crystal I am using as my clock input.

V1, that worked had ELF values of 470 pF, 2.55k, and 22 nF.

Can you provide me with good ELF values given how I have this chip set up? Do you know why V2 is having trouble and V1 isn't? When I changed the values of V2 closer to that of V1 with what 0201 parts I had lying around, my sampling scope showed that the output would sometimes become not noisy, like something was on the verge of being stable. Any ideas?

Thanks,

Matt