Part Number: LMK04828

Hi,

The following clock generator (Part#: LMK04828BISQ)is used in one of our application.100MHz clock is derived for DUT.

Observation:

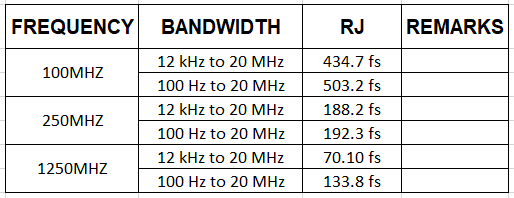

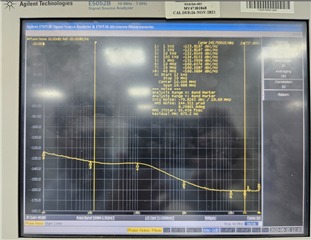

It is observed that the random jitter is around 700fs in our board. However, the datasheet states that "88fs RMS jitter for 12KHz to 20MHz & 91fs RMS jitter for 100Hz to 20MHz.

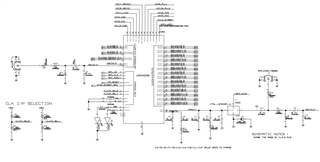

Schematic and Register setting details are attached.

Please review the schematic and register setting details and let us know your suggestions to reduce the jitter in our design.

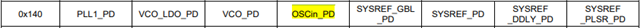

***************** ECMB:LMK04828:Registers ************** RESET 10 NA2 0 SPI_3WIRE_DIS 0x1 NA1 0 RESET 0 POWERDOWN 00 POWERDOWN 0 NA 0 ID_DEVICE_TYPE 06 ID_DEVICE_TYPE 0x6 ID_PROD_15_8 d0 ID_PROD_15_8 0xd0 ID_PROD 5b ID_PROD 0x5b ID_MASKREV 20 ID_MASKREV 0x20 ID_VNDR_15_8 51 ID_VNDR_15_8 0x51 ID_VNDR 04 ID_VNDR 0x4 DCLKout0_DIV 19 DCLKout0_DIV 0x19 CLKout0_1_IDL 0 CLKout0_1_ODL 0 NA 0 DCLKout2_DIV 19 DCLKout2_DIV 0x19 CLKout2_3_IDL 0 CLKout2_3_ODL 0 NA 0 DCLKout4_DIV 00 DCLKout4_DIV 0 CLKout4_5_IDL 0 CLKout4_5_ODL 0 NA 0 DCLKout6_DIV 05 DCLKout6_DIV 0x5 CLKout6_7_IDL 0 CLKout6_7_ODL 0 NA 0 DCLKout8_DIV 00 DCLKout8_DIV 0 CLKout8_9_IDL 0 CLKout8_9_ODL 0 NA 0 DCLKout10_DIV 00 DCLKout10_DIV 0 CLKout10_11_IDL 0 CLKout10_11_ODL 0 NA 0 DCLKout12_DIV 19 DCLKout12_DIV 0x19 CLKout12_13_IDL 0 CLKout12_13_ODL 0 NA 0 DCLKout0_DDLY_CNT 55 DCLKout0_DDLY_CNTL 0x5 DCLKout0_DDLY_CNTH 0x5 DCLKout2_DDLY_CNT 55 DCLKout2_DDLY_CNTL 0x5 DCLKout2_DDLY_CNTH 0x5 DCLKout4_DDLY_CNT 55 DCLKout4_DDLY_CNTL 0x5 DCLKout4_DDLY_CNTH 0x5 DCLKout6_DDLY_CNT 55 DCLKout6_DDLY_CNTL 0x5 DCLKout6_DDLY_CNTH 0x5 DCLKout8_DDLY_CNT 55 DCLKout8_DDLY_CNTL 0x5 DCLKout8_DDLY_CNTH 0x5 DCLKout10_DDLY_CNT 55 DCLKout10_DDLY_CNTL 0x5 DCLKout10_DDLY_CNTH 0x5 DCLKout12_DDLY_CNT 55 DCLKout12_DDLY_CNTL 0x5 DCLKout12_DDLY_CNTH 0x5 DCLKout0_ADLY 07 DCLKout0_MUX 0x3 DCLKout0_ALDY_MUX 0x1 DCLKout0_ALDY 0 DCLKout2_ADLY 07 DCLKout2_MUX 0x3 DCLKout2_ALDY_MUX 0x1 DCLKout2_ALDY 0 DCLKout4_ADLY 03 DCLKout4_MUX 0x3 DCLKout4_ALDY_MUX 0 DCLKout4_ALDY 0 DCLKout6_ADLY 07 DCLKout6_MUX 0x3 DCLKout6_ALDY_MUX 0x1 DCLKout6_ALDY 0 DCLKout8_ADLY 03 DCLKout8_MUX 0x3 DCLKout8_ALDY_MUX 0 DCLKout8_ALDY 0 DCLKout10_ADLY 03 DCLKout10_MUX 0x3 DCLKout10_ALDY_MUX 0 DCLKout10_ALDY 0 DCLKout12_ADLY 07 DCLKout12_MUX 0x3 DCLKout12_ALDY_MUX 0x1 DCLKout12_ALDY 0 SDCLKout1_MUX 00 SDCLKout1_HS 0 SDCLKout1_DDLY 0 SDCLKout1_MUX 0 DCLKout0_HS 0 NA 0 SDCLKout3_MUX 00 SDCLKout3_HS 0 SDCLKout3_DDLY 0 SDCLKout3_MUX 0 DCLKout2_HS 0 NA 0 SDCLKout5_MUX 00 SDCLKout5_HS 0 SDCLKout5_DDLY 0 SDCLKout5_MUX 0 DCLKout4_HS 0 NA 0 SDCLKout7_MUX 00 SDCLKout7_HS 0 SDCLKout7_DDLY 0 SDCLKout7_MUX 0 DCLKout6_HS 0 NA 0 SDCLKout9_MUX 00 SDCLKout9_HS 0 SDCLKout9_DDLY 0 SDCLKout8_MUX 0 DCLKout8_HS 0 NA 0 SDCLKout11_MUX 00 SDCLKout11_HS 0 SDCLKout11_DDLY 0 SDCLKout11_MUX 0 DCLKout10_HS 0 NA 0 SDCLKout13_MUX 00 SDCLKout13_HS 0 SDCLKout13_DDLY 0 SDCLKout13_MUX 0 DCLKout12_HS 0 NA 0 SDCLKout1_ADLY 00 SDCLKout1_ADLY 0 SDCLKout1_ADLY_EN 0 NA 0 SDCLKout3_ADLY 00 SDCLKout3_ADLY 0 SDCLKout3_ADLY_EN 0 NA 0 SDCLKout5_ADLY 00 SDCLKout5_ADLY 0 SDCLKout5_ADLY_EN 0 NA 0 SDCLKout7_ADLY 00 SDCLKout7_ADLY 0 SDCLKout7_ADLY_EN 0 NA 0 SDCLKout9_ADLY 00 SDCLKout9_ADLY 0 SDCLKout9_ADLY_EN 0 NA 0 SDCLKout11_ADLY 00 SDCLKout11_ADLY 0 SDCLKout11_ADLY_EN 0 NA 0 SDCLKout13_ADLY 00 SDCLKout13_ADLY 0 SDCLKout13_ADLY_EN 0 NA 0 DCLKout0_DDLY_PD 60 SDCLKout1_PD 0 SDCLKout1_DIS_MODE 0 CLKout0_1_PD 0 DCLKout0_ADLY_PD 0 DCLKout0_ADLYg_PD 0x1 DCLKout0_HSg_PD 0x1 DCLKout0_DDLY_PD 0 DCLKout2_DDLY_PD 60 SDCLKout3_PD 0 SDCLKout3_DIS_MODE 0 CLKout2_3_PD 0 DCLKout2_ADLY_PD 0 DCLKout2_ADLYg_PD 0x1 DCLKout2_HSg_PD 0x1 DCLKout2_DDLY_PD 0 DCLKout4_DDLY_PD 68 SDCLKout5_PD 0 SDCLKout5_DIS_MODE 0 CLKout4_5_PD 0x1 DCLKout4_ADLY_PD 0 DCLKout4_ADLYg_PD 0x1 DCLKout4_HSg_PD 0x1 DCLKout4_DDLY_PD 0 DCLKout6_DDLY_PD 70 SDCLKout7_PD 0 SDCLKout7_DIS_MODE 0 CLKout6_7_PD 0 DCLKout6_ADLY_PD 0x1 DCLKout6_ADLYg_PD 0x1 DCLKout6_HSg_PD 0x1 DCLKout6_DDLY_PD 0 DCLKout8_DDLY_PD 68 SDCLKout9_PD 0 SDCLKout9_DIS_MODE 0 CLKout8_9_PD 0x1 DCLKout8_ADLY_PD 0 DCLKout8_ADLYg_PD 0x1 DCLKout8_HSg_PD 0x1 DCLKout8_DDLY_PD 0 DCLKout10_DDLY_PD 68 SDCLKout11_PD 0 SDCLKout11_DIS_MODE 0 CLKout10_11_PD 0x1 DCLKout10_ADLY_PD 0 DCLKout10_ADLYg_PD 0x1 DCLKout10_HSg_PD 0x1 DCLKout10_DDLY_PD 0 DCLKout12_DDLY_PD 60 SDCLKout13_PD 0 SDCLKout13_DIS_MODE 0 CLKout12_13_PD 0 DCLKout12_ADLY_PD 0 DCLKout12_ADLYg_PD 0x1 DCLKout12_HSg_PD 0x1 DCLKout12_DDLY_PD 0 SDCLKout1_POL 06 DCLKout0_FMT 0x6 DCLKout0_POL 0 SDCLKout1_FMT 0 SDCLKout1_POL 0 SDCLKout3_POL 06 DCLKout2_FMT 0x6 DCLKout2_POL 0 SDCLKout3_FMT 0 SDCLKout3_POL 0 SDCLKout5_POL 00 DCLKout4_FMT 0 DCLKout4_POL 0 SDCLKout5_FMT 0 SDCLKout5_POL 0 SDCLKout7_POL 06 DCLKout6_FMT 0x6 DCLKout6_POL 0 SDCLKout7_FMT 0 SDCLKout7_POL 0 SDCLKout9_POL 00 DCLKout8_FMT 0 DCLKout8_POL 0 SDCLKout9_FMT 0 SDCLKout9_POL 0 SDCLKout11_POL 00 DCLKout10_FMT 0 DCLKout10_POL 0 SDCLKout11_FMT 0 SDCLKout11_POL 0 SDCLKout13_POL 06 DCLKout12_FMT 0x6 DCLKout12_POL 0 SDCLKout13_FMT 0 SDCLKout13_POL 0 VCO_MUX 04 OSCout_FMT 0x4 OSCout_MUX 0 VCO_MUX 0 NA 0 SYSREF_MUX 00 SYSREF_MUX 0 NA 0 SYSREF_DIV_12_8 0c SYSREF_DIV_12_8 0xc NA 0 SYSREF_DIV_7_0 00 SYSREF_DIV_7_0 0 SYSREF_DDLY_12_8 00 SYSREF_DDLY_12_8 0 NA 0 SYSREF_DDLY_7_0 08 SYSREF_DDLY_7_0 0x8 SYSREF_PULSE_CNT 03 NA 0 SYSREF_PULSE_CNT 0x3 PLL2_NCLK_MUX 00 NA 0 PLL2_NCLK_MUX 0 PLL1_NCLK_MUX 0 FB_MUX 0 FB_MUX_EN 0 PLL1_PD 07 PLL1_PD 0 VCO_LDO_PD 0 VCO_PD 0 OSCin_PD 0 SYSREF_GBL_PD 0 SYSREF_PD 0x1 SYSREF_DDLY_PD 0x1 SYSREF_PLSR_PD 0x1 DDLYdSYSREF_EN 00 DDLYd _SYSREF_EN 0 DDLYd12_EN 0 DDLYd10_EN 0 DDLYd8_EN 0 DDLYd6_EN 0 DDLYd4_EN 0 DDLYd2_EN 0 DDLYd0_EN 0 DDLYd_STEP_CNT 00 NA 0 DDLYd_STEP_CNT 0 SYSREF_CLR 91 SYSREF_CLR 0x1 SYNC_1SHOT_EN 0 SYNC_POL 0 SYNC_EN 0x1 SYNC_PLL2_DLD 0 SYNC_PLL1_DLD 0 SYNC_MODE 0x1 SYNC_DISX 00 SYNC_DISSYSREF 0 SYNC_DIS12 0 SYNC_DIS10 0 SYNC_DIS8 0 SYNC_DIS6 0 SYNC_DIS4 0 SYNC_DIS2 0 SYNC_DIS0 0 FIXED_REGISTER 00 Fixed_Register 0 CLKin2_EN 18 NA 0 CLKin2_EN 0 CLKin1_EN 0x1 CLKin0_EN 0x1 CLKin2_TYPE 0 CLKin1_TYPE 0 CLKin0_TYPE 0 CLKin_SEL_POL 3a CLKin_SEL_POL 0 CLKin_SEL_MODE 0x3 CLKin1_OUT_MUX 0x2 CLKin0_OUT_MUX 0x2 CLKin_SEL0_MUX 02 NA 0 CLKin_SEL0_MUX 0 CLKin_SEL0_TYPE 0x2 CLKin_SEL1_MUX 33 NA 0 SDIO_RDBK_TYPE 0 CLKin_SEL1_MUX 0x6 CLKin_SEL1_TYPE 0x3 RESET_MUX 02 NA 0 RESET_MUX 0 RESET_TYPE 0x2 LOS_TIMEOUT 16 LOS_TIMEOUT 0 LOS_EN 0 TRACK_EN 0x1 HOLDOVER_FORCE 0 MAN_DAC_EN 0x1 MAN_DAC_9_8 0x2 MAN_DAC_9_8 16 LOS_TIMEOUT 0 LOS_EN 0 TRACK_EN 0x1 HOLDOVER_FORCE 0 MAN_DAC_EN 0x1 MAN_DAC_9_8 0x2 MAN_DAC_7_0 00 MAN_DAC_7_0 0 DAC_TRIP_LOW 00 NA 0 DAC_TRIP_LOW 0 DAC_CLK_MULT 00 DAC_CLK_MULT 0 DAC_TRIP_HIGH 0 DAC_CLK_CNTR 7f DAC_CLK_CNTR 0x7f HOLDOVER_PLL1_DET 03 NA 0 HOLDOVER_PLL1_DET 0 HOLDOVER_LOS_DET 0 HOLDOVER_VTUNE_DET 0 HOLDOVER_HITLESS_SWITCH 0x1 HOLDOVER_EN 0x1 HOLDOVER_DLD_CNT_13_8 02 NA 0 HOLDOVER_DLD_CNT_13_8 0x2 HOLDOVER_DLD_CNT_7_0 00 HOLDOVER_DLD_CNT_7_0 0 CLKin0_R_13_8 00 NA 0 CLKin0_R_13_8 0 CLKin0_R_7_0 78 CLKin0_R_7_0 0x78 CLKin1_R_13_0 00 NA 0 CLKin1_R_13_8 0 CLKin1_R_7_0 96 CLKin1_R_7_0 0x96 CLKin2_R_13_8 00 NA 0 CLKin2_R_13_8 0 CLKin2_R_7_0 96 CLKin2_R_7_0 0 PLL1_N_13_8 00 NA 0 PLL1_N_13_8 0 PLL1_N_7_0 78 PLL1_N_7_0 0x78 PLL1_WND_SIZE d4 PLL1_WND_SIZE 0x3 PLL1_CP_TRI 0 PLL1_CP_POL 0x1 PLL1_CP_GAIN 0x4 PLL1_DLD_CNT_13_8 20 NA 0 PLL1_DLD_CNT_13_8 0x20 PLL1_DLD_CNT_7_0 00 PLL1_DLD_CNT_7_0 0 PLL1_R_DLY 00 NA 0 PLL1_R_DLY 0 PLL1_N_DLY 0 PLL1_LD_MUX 0e PLL1_LD_MUX 0x1 PLL1_LD_TYPE 0x6 PLL2_R_11_8 00 NA 0 PLL2_R_11_8 0 PLL2_R_7_0 02 PLL2_R_7_0 0x2 PLL2_P 44 PLL2_P 0x2 OSCin_FREQ 0x1 PLL2_XTAL_EN 0 PLL2_REF_2X_EN 0 PLL2_N_CAL_17_16 00 NA 0 PLL2_N_CAL_17_16 0 PLL2_N_CAL_15_8 00 PLL2_N_CAL_15_8 0 PLL2_N_CAL_7_0 0c PLL2_N_CAL_7_0 0xc PLL2_N_17_16 00 NA 0 PLL2_FCAL_DIS 0 PLL2_N_17_16 0 PLL2_N_15_8 00 PLL2_N_15_8 0 PLL2_N_7_0 19 PLL2_N_7_0 0x19 PLL2_WND_SIZE 59 NA 0 PLL2_WND_SIZE 0x2 PLL2_CP_GAIN 0x3 PLL2_CP_POL 0 PLL2_CP_TRI 0 Fixed Value 0x1 PLL2_DLD_CNT_13_8 20 NA 0 SYSREF_REQ_EN 0 PLL2_DLD_CNT_13_8 0x20 PLL2_DLD_CNT_7_0 00 PLL2_DLD_CNT 0 PLL2_LF_R4 00 NA 0 PLL2_LF_R4 0 PLL2_LF_R3 0 PLL2_LF_C4 00 PLL2_LF_C4 0 PLL2_LF_C3 0 PLL2_LD_MUX 13 PLL2_LD_MUX 0x2 PLL2_LD_TYPE 0x3 PLL2_PRE_PD 00 NA 0 PLL2_PRE_PD 0 PLL2_PD 0 NA 0 OPT_REG_1 15 OPT_REG_1 0x15 OPT_REG_2 33 OPT_REG_2 0x33 RB_PLL1_LD_LOST 00 NA 0 RB_PLL1_LD_LOST 0 RB_PLL1_LD 0 CLR_PLL1_LD_LOST 0 RB_PLL2_LD_LOST 06 NA 0 RB_PLL2_LD_LOST 0x1 RB_PLL2_LD 0x1 CLR_PLL2_LD_LOST 0 RB_DAC_VALUE_MSB 90 RB_DAC_VALUE_9_8 0x2 RB_CLKin2_SEL 0 RB_CLKin1_SEL 0x1 RB_CLKin0_SEL 0 NA 0 RB_CLKin1_LOS 0 RB_CLKin0_LOS 0 RB_DAC_VALUE 00 RB_DAC_VALUE_7_0 0 RB_HOLDOVER 10 NA 0 RB_HOLDOVER 0x1 NA 0 SPI_LOCK_23_16 00 SPI_LOCK_23_16 0 SPI_LOCK_15_8 00 SPI_LOCK_15_8 0 SPI_LOCK_7_0 00 SPI_LOCK_7_0 0 ***************** ECMB:LMK04828 ************** RESET 10 NA2 0 SPI_3WIRE_DIS 0x1 NA1 0 RESET 0 POWERDOWN 00 POWERDOWN 0 NA 0 ID_DEVICE_TYPE 06 ID_DEVICE_TYPE 0x6 ID_PROD_15_8 d0 ID_PROD_15_8 0xd0 ID_PROD 5b ID_PROD 0x5b ID_MASKREV 20 ID_MASKREV 0x20 ID_VNDR_15_8 51 ID_VNDR_15_8 0x51 ID_VNDR 04 ID_VNDR 0x4 DCLKout0_DIV 19 DCLKout0_DIV 0x19 CLKout0_1_IDL 0 CLKout0_1_ODL 0 NA 0 DCLKout2_DIV 19 DCLKout2_DIV 0x19 CLKout2_3_IDL 0 CLKout2_3_ODL 0 NA 0 DCLKout4_DIV 00 DCLKout4_DIV 0 CLKout4_5_IDL 0 CLKout4_5_ODL 0 NA 0 DCLKout6_DIV 05 DCLKout6_DIV 0x5 CLKout6_7_IDL 0 CLKout6_7_ODL 0 NA 0 DCLKout8_DIV 00 DCLKout8_DIV 0 CLKout8_9_IDL 0 CLKout8_9_ODL 0 NA 0 DCLKout10_DIV 00 DCLKout10_DIV 0 CLKout10_11_IDL 0 CLKout10_11_ODL 0 NA 0 DCLKout12_DIV 19 DCLKout12_DIV 0x19 CLKout12_13_IDL 0 CLKout12_13_ODL 0 NA 0 DCLKout0_DDLY_CNT 55 DCLKout0_DDLY_CNTL 0x5 DCLKout0_DDLY_CNTH 0x5 DCLKout2_DDLY_CNT 55 DCLKout2_DDLY_CNTL 0x5 DCLKout2_DDLY_CNTH 0x5 DCLKout4_DDLY_CNT 55 DCLKout4_DDLY_CNTL 0x5 DCLKout4_DDLY_CNTH 0x5 DCLKout6_DDLY_CNT 55 DCLKout6_DDLY_CNTL 0x5 DCLKout6_DDLY_CNTH 0x5 DCLKout8_DDLY_CNT 55 DCLKout8_DDLY_CNTL 0x5 DCLKout8_DDLY_CNTH 0x5 DCLKout10_DDLY_CNT 55 DCLKout10_DDLY_CNTL 0x5 DCLKout10_DDLY_CNTH 0x5 DCLKout12_DDLY_CNT 55 DCLKout12_DDLY_CNTL 0x5 DCLKout12_DDLY_CNTH 0x5 DCLKout0_ADLY 07 DCLKout0_MUX 0x3 DCLKout0_ALDY_MUX 0x1 DCLKout0_ALDY 0 DCLKout2_ADLY 07 DCLKout2_MUX 0x3 DCLKout2_ALDY_MUX 0x1 DCLKout2_ALDY 0 DCLKout4_ADLY 03 DCLKout4_MUX 0x3 DCLKout4_ALDY_MUX 0 DCLKout4_ALDY 0 DCLKout6_ADLY 07 DCLKout6_MUX 0x3 DCLKout6_ALDY_MUX 0x1 DCLKout6_ALDY 0 DCLKout8_ADLY 03 DCLKout8_MUX 0x3 DCLKout8_ALDY_MUX 0 DCLKout8_ALDY 0 DCLKout10_ADLY 03 DCLKout10_MUX 0x3 DCLKout10_ALDY_MUX 0 DCLKout10_ALDY 0 DCLKout12_ADLY 07 DCLKout12_MUX 0x3 DCLKout12_ALDY_MUX 0x1 DCLKout12_ALDY 0 SDCLKout1_MUX 00 SDCLKout1_HS 0 SDCLKout1_DDLY 0 SDCLKout1_MUX 0 DCLKout0_HS 0 NA 0 SDCLKout3_MUX 00 SDCLKout3_HS 0 SDCLKout3_DDLY 0 SDCLKout3_MUX 0 DCLKout2_HS 0 NA 0 SDCLKout5_MUX 00 SDCLKout5_HS 0 SDCLKout5_DDLY 0 SDCLKout5_MUX 0 DCLKout4_HS 0 NA 0 SDCLKout7_MUX 00 SDCLKout7_HS 0 SDCLKout7_DDLY 0 SDCLKout7_MUX 0 DCLKout6_HS 0 NA 0 SDCLKout9_MUX 00 SDCLKout9_HS 0 SDCLKout9_DDLY 0 SDCLKout8_MUX 0 DCLKout8_HS 0 NA 0 SDCLKout11_MUX 00 SDCLKout11_HS 0 SDCLKout11_DDLY 0 SDCLKout11_MUX 0 DCLKout10_HS 0 NA 0 SDCLKout13_MUX 00 SDCLKout13_HS 0 SDCLKout13_DDLY 0 SDCLKout13_MUX 0 DCLKout12_HS 0 NA 0 SDCLKout1_ADLY 00 SDCLKout1_ADLY 0 SDCLKout1_ADLY_EN 0 NA 0 SDCLKout3_ADLY 00 SDCLKout3_ADLY 0 SDCLKout3_ADLY_EN 0 NA 0 SDCLKout5_ADLY 00 SDCLKout5_ADLY 0 SDCLKout5_ADLY_EN 0 NA 0 SDCLKout7_ADLY 00 SDCLKout7_ADLY 0 SDCLKout7_ADLY_EN 0 NA 0 SDCLKout9_ADLY 00 SDCLKout9_ADLY 0 SDCLKout9_ADLY_EN 0 NA 0 SDCLKout11_ADLY 00 SDCLKout11_ADLY 0 SDCLKout11_ADLY_EN 0 NA 0 SDCLKout13_ADLY 00 SDCLKout13_ADLY 0 SDCLKout13_ADLY_EN 0 NA 0 DCLKout0_DDLY_PD 60 SDCLKout1_PD 0 SDCLKout1_DIS_MODE 0 CLKout0_1_PD 0 DCLKout0_ADLY_PD 0 DCLKout0_ADLYg_PD 0x1 DCLKout0_HSg_PD 0x1 DCLKout0_DDLY_PD 0 DCLKout2_DDLY_PD 60 SDCLKout3_PD 0 SDCLKout3_DIS_MODE 0 CLKout2_3_PD 0 DCLKout2_ADLY_PD 0 DCLKout2_ADLYg_PD 0x1 DCLKout2_HSg_PD 0x1 DCLKout2_DDLY_PD 0 DCLKout4_DDLY_PD 68 SDCLKout5_PD 0 SDCLKout5_DIS_MODE 0 CLKout4_5_PD 0x1 DCLKout4_ADLY_PD 0 DCLKout4_ADLYg_PD 0x1 DCLKout4_HSg_PD 0x1 DCLKout4_DDLY_PD 0 DCLKout6_DDLY_PD 70 SDCLKout7_PD 0 SDCLKout7_DIS_MODE 0 CLKout6_7_PD 0 DCLKout6_ADLY_PD 0x1 DCLKout6_ADLYg_PD 0x1 DCLKout6_HSg_PD 0x1 DCLKout6_DDLY_PD 0 DCLKout8_DDLY_PD 68 SDCLKout9_PD 0 SDCLKout9_DIS_MODE 0 CLKout8_9_PD 0x1 DCLKout8_ADLY_PD 0 DCLKout8_ADLYg_PD 0x1 DCLKout8_HSg_PD 0x1 DCLKout8_DDLY_PD 0 DCLKout10_DDLY_PD 68 SDCLKout11_PD 0 SDCLKout11_DIS_MODE 0 CLKout10_11_PD 0x1 DCLKout10_ADLY_PD 0 DCLKout10_ADLYg_PD 0x1 DCLKout10_HSg_PD 0x1 DCLKout10_DDLY_PD 0 DCLKout12_DDLY_PD 60 SDCLKout13_PD 0 SDCLKout13_DIS_MODE 0 CLKout12_13_PD 0 DCLKout12_ADLY_PD 0 DCLKout12_ADLYg_PD 0x1 DCLKout12_HSg_PD 0x1 DCLKout12_DDLY_PD 0 SDCLKout1_POL 06 DCLKout0_FMT 0x6 DCLKout0_POL 0 SDCLKout1_FMT 0 SDCLKout1_POL 0 SDCLKout3_POL 06 DCLKout2_FMT 0x6 DCLKout2_POL 0 SDCLKout3_FMT 0 SDCLKout3_POL 0 SDCLKout5_POL 00 DCLKout4_FMT 0 DCLKout4_POL 0 SDCLKout5_FMT 0 SDCLKout5_POL 0 SDCLKout7_POL 06 DCLKout6_FMT 0x6 DCLKout6_POL 0 SDCLKout7_FMT 0 SDCLKout7_POL 0 SDCLKout9_POL 00 DCLKout8_FMT 0 DCLKout8_POL 0 SDCLKout9_FMT 0 SDCLKout9_POL 0 SDCLKout11_POL 00 DCLKout10_FMT 0 DCLKout10_POL 0 SDCLKout11_FMT 0 SDCLKout11_POL 0 SDCLKout13_POL 06 DCLKout12_FMT 0x6 DCLKout12_POL 0 SDCLKout13_FMT 0 SDCLKout13_POL 0 VCO_MUX 04 OSCout_FMT 0x4 OSCout_MUX 0 VCO_MUX 0 NA 0 SYSREF_MUX 00 SYSREF_MUX 0 NA 0 SYSREF_DIV_12_8 0c SYSREF_DIV_12_8 0xc NA 0 SYSREF_DIV_7_0 00 SYSREF_DIV_7_0 0 SYSREF_DDLY_12_8 00 SYSREF_DDLY_12_8 0 NA 0 SYSREF_DDLY_7_0 08 SYSREF_DDLY_7_0 0x8 SYSREF_PULSE_CNT 03 NA 0 SYSREF_PULSE_CNT 0x3 PLL2_NCLK_MUX 00 NA 0 PLL2_NCLK_MUX 0 PLL1_NCLK_MUX 0 FB_MUX 0 FB_MUX_EN 0 PLL1_PD 07 PLL1_PD 0 VCO_LDO_PD 0 VCO_PD 0 OSCin_PD 0 SYSREF_GBL_PD 0 SYSREF_PD 0x1 SYSREF_DDLY_PD 0x1 SYSREF_PLSR_PD 0x1 DDLYdSYSREF_EN 00 DDLYd _SYSREF_EN 0 DDLYd12_EN 0 DDLYd10_EN 0 DDLYd8_EN 0 DDLYd6_EN 0 DDLYd4_EN 0 DDLYd2_EN 0 DDLYd0_EN 0 DDLYd_STEP_CNT 00 NA 0 DDLYd_STEP_CNT 0 SYSREF_CLR 91 SYSREF_CLR 0x1 SYNC_1SHOT_EN 0 SYNC_POL 0 SYNC_EN 0x1 SYNC_PLL2_DLD 0 SYNC_PLL1_DLD 0 SYNC_MODE 0x1 SYNC_DISX 00 SYNC_DISSYSREF 0 SYNC_DIS12 0 SYNC_DIS10 0 SYNC_DIS8 0 SYNC_DIS6 0 SYNC_DIS4 0 SYNC_DIS2 0 SYNC_DIS0 0 FIXED_REGISTER 00 Fixed_Register 0 CLKin2_EN 18 NA 0 CLKin2_EN 0 CLKin1_EN 0x1 CLKin0_EN 0x1 CLKin2_TYPE 0 CLKin1_TYPE 0 CLKin0_TYPE 0 CLKin_SEL_POL 3a CLKin_SEL_POL 0 CLKin_SEL_MODE 0x3 CLKin1_OUT_MUX 0x2 CLKin0_OUT_MUX 0x2 CLKin_SEL0_MUX 02 NA 0 CLKin_SEL0_MUX 0 CLKin_SEL0_TYPE 0x2 CLKin_SEL1_MUX 33 NA 0 SDIO_RDBK_TYPE 0 CLKin_SEL1_MUX 0x6 CLKin_SEL1_TYPE 0x3 RESET_MUX 02 NA 0 RESET_MUX 0 RESET_TYPE 0x2 LOS_TIMEOUT 16 LOS_TIMEOUT 0 LOS_EN 0 TRACK_EN 0x1 HOLDOVER_FORCE 0 MAN_DAC_EN 0x1 MAN_DAC_9_8 0x2 MAN_DAC_9_8 16 LOS_TIMEOUT 0 LOS_EN 0 TRACK_EN 0x1 HOLDOVER_FORCE 0 MAN_DAC_EN 0x1 MAN_DAC_9_8 0x2 MAN_DAC_7_0 00 MAN_DAC_7_0 0 DAC_TRIP_LOW 00 NA 0 DAC_TRIP_LOW 0 DAC_CLK_MULT 00 DAC_CLK_MULT 0 DAC_TRIP_HIGH 0 DAC_CLK_CNTR 7f DAC_CLK_CNTR 0x7f HOLDOVER_PLL1_DET 03 NA 0 HOLDOVER_PLL1_DET 0 HOLDOVER_LOS_DET 0 HOLDOVER_VTUNE_DET 0 HOLDOVER_HITLESS_SWITCH 0x1 HOLDOVER_EN 0x1 HOLDOVER_DLD_CNT_13_8 02 NA 0 HOLDOVER_DLD_CNT_13_8 0x2 HOLDOVER_DLD_CNT_7_0 00 HOLDOVER_DLD_CNT_7_0 0 CLKin0_R_13_8 00 NA 0 CLKin0_R_13_8 0 CLKin0_R_7_0 78 CLKin0_R_7_0 0x78 CLKin1_R_13_0 00 NA 0 CLKin1_R_13_8 0 CLKin1_R_7_0 96 CLKin1_R_7_0 0x96 CLKin2_R_13_8 00 NA 0 CLKin2_R_13_8 0 CLKin2_R_7_0 96 CLKin2_R_7_0 0 PLL1_N_13_8 00 NA 0 PLL1_N_13_8 0 PLL1_N_7_0 78 PLL1_N_7_0 0x78 PLL1_WND_SIZE d4 PLL1_WND_SIZE 0x3 PLL1_CP_TRI 0 PLL1_CP_POL 0x1 PLL1_CP_GAIN 0x4 PLL1_DLD_CNT_13_8 20 NA 0 PLL1_DLD_CNT_13_8 0x20 PLL1_DLD_CNT_7_0 00 PLL1_DLD_CNT_7_0 0 PLL1_R_DLY 00 NA 0 PLL1_R_DLY 0 PLL1_N_DLY 0 PLL1_LD_MUX 0e PLL1_LD_MUX 0x1 PLL1_LD_TYPE 0x6 PLL2_R_11_8 00 NA 0 PLL2_R_11_8 0 PLL2_R_7_0 02 PLL2_R_7_0 0x2 PLL2_P 44 PLL2_P 0x2 OSCin_FREQ 0x1 PLL2_XTAL_EN 0 PLL2_REF_2X_EN 0 PLL2_N_CAL_17_16 00 NA 0 PLL2_N_CAL_17_16 0 PLL2_N_CAL_15_8 00 PLL2_N_CAL_15_8 0 PLL2_N_CAL_7_0 0c PLL2_N_CAL_7_0 0xc PLL2_N_17_16 00 NA 0 PLL2_FCAL_DIS 0 PLL2_N_17_16 0 PLL2_N_15_8 00 PLL2_N_15_8 0 PLL2_N_7_0 19 PLL2_N_7_0 0x19 PLL2_WND_SIZE 59 NA 0 PLL2_WND_SIZE 0x2 PLL2_CP_GAIN 0x3 PLL2_CP_POL 0 PLL2_CP_TRI 0 Fixed Value 0x1 PLL2_DLD_CNT_13_8 20 NA 0 SYSREF_REQ_EN 0 PLL2_DLD_CNT_13_8 0x20 PLL2_DLD_CNT_7_0 00 PLL2_DLD_CNT 0 PLL2_LF_R4 00 NA 0 PLL2_LF_R4 0 PLL2_LF_R3 0 PLL2_LF_C4 00 PLL2_LF_C4 0 PLL2_LF_C3 0 PLL2_LD_MUX 13 PLL2_LD_MUX 0x2 PLL2_LD_TYPE 0x3 PLL2_PRE_PD 00 NA 0 PLL2_PRE_PD 0 PLL2_PD 0 NA 0 OPT_REG_1 15 OPT_REG_1 0x15 OPT_REG_2 33 OPT_REG_2 0x33 RB_PLL1_LD_LOST 00 NA 0 RB_PLL1_LD_LOST 0 RB_PLL1_LD 0 CLR_PLL1_LD_LOST 0 RB_PLL2_LD_LOST 06 NA 0 RB_PLL2_LD_LOST 0x1 RB_PLL2_LD 0x1 CLR_PLL2_LD_LOST 0 RB_DAC_VALUE_MSB 90 RB_DAC_VALUE_9_8 0x2 RB_CLKin2_SEL 0 RB_CLKin1_SEL 0x1 RB_CLKin0_SEL 0 NA 0 RB_CLKin1_LOS 0 RB_CLKin0_LOS 0 RB_DAC_VALUE 00 RB_DAC_VALUE_7_0 0 RB_HOLDOVER 10 NA 0 RB_HOLDOVER 0x1 NA 0 SPI_LOCK_23_16 00 SPI_LOCK_23_16 0 SPI_LOCK_15_8 00 SPI_LOCK_15_8 0 SPI_LOCK_7_0 00 SPI_LOCK_7_0 0

Thank you,

Dhanasekaran.V