Hello Team,

can you provide the switching time when using IN_SEL to gate a 2MHz clock at IN0 while setting IN1=0, please? This timing is not specified in the data sheet.

Also, will the switching be glitch free?

Thank you and Best Regards, Hans

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello Team,

can you provide the switching time when using IN_SEL to gate a 2MHz clock at IN0 while setting IN1=0, please? This timing is not specified in the data sheet.

Also, will the switching be glitch free?

Thank you and Best Regards, Hans

Hi Hans,

Switching time is less than 10 ns in AC coupled outputs mode. I would expect similar in DC coupled mode or better.

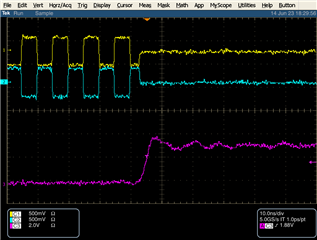

Below is a screenshot of CDCLVP1204 output switching from INP0 (100 MHz) to INP1 ( No clock).

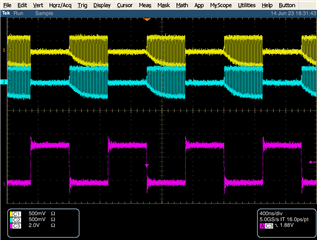

There is no glitch on the transition. Since this is AC coupled output you would see that outputs take time to settle in Figure 2.

Figure 1.

Figure 2.

Best,

Asim