Part Number: LMK5C33216EVM

Other Parts Discussed in Thread: LMK5C33216,

Hi team,

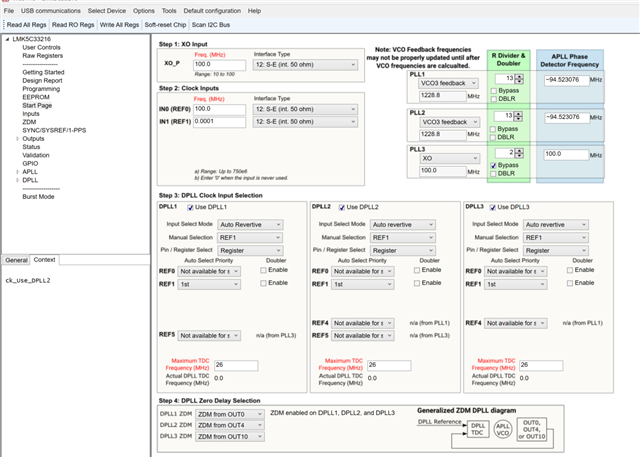

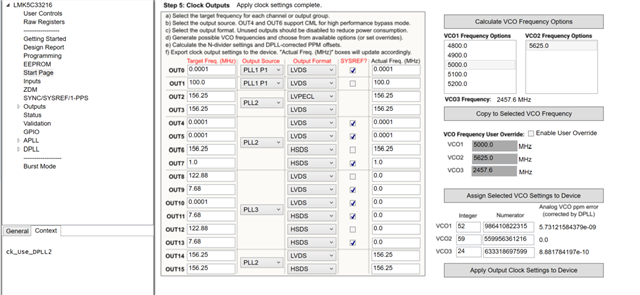

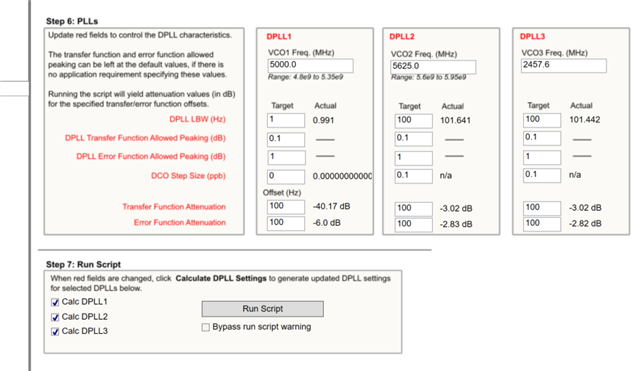

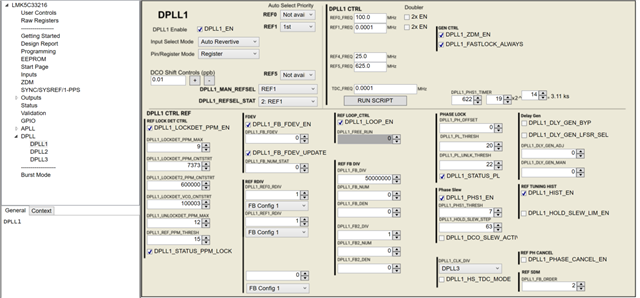

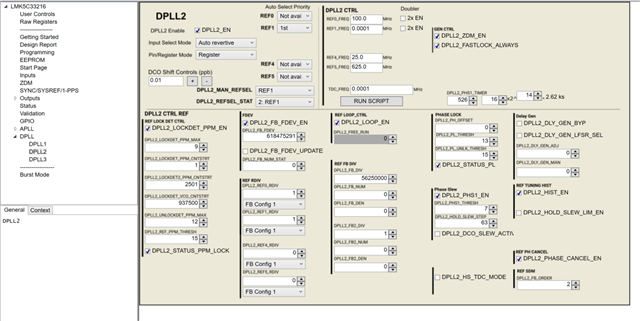

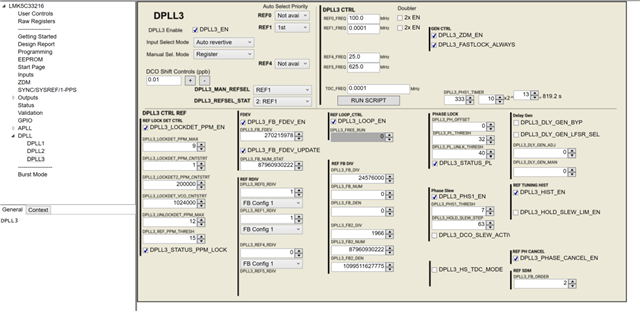

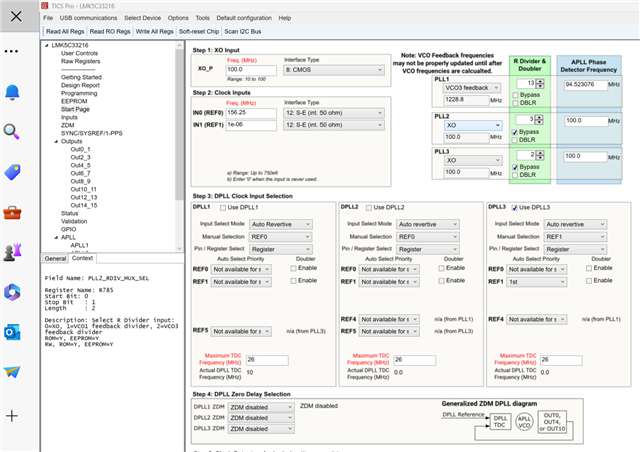

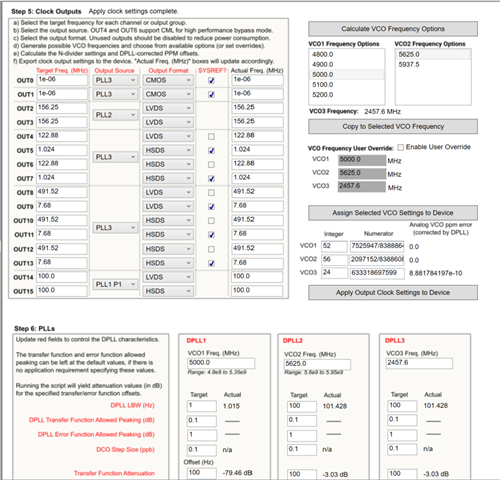

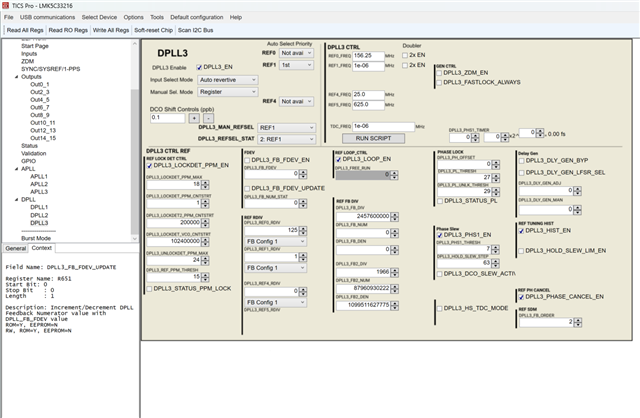

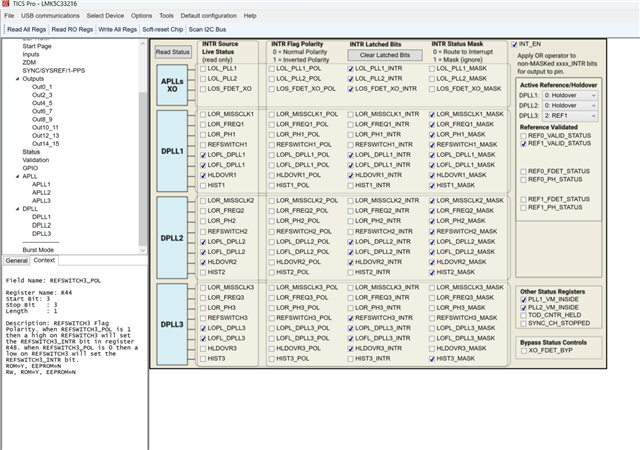

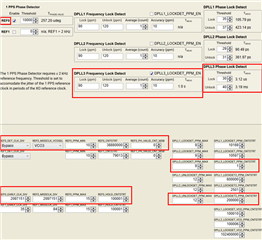

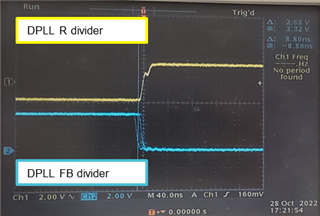

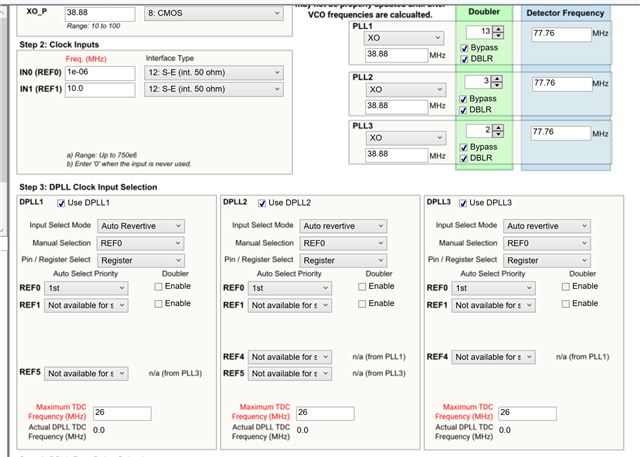

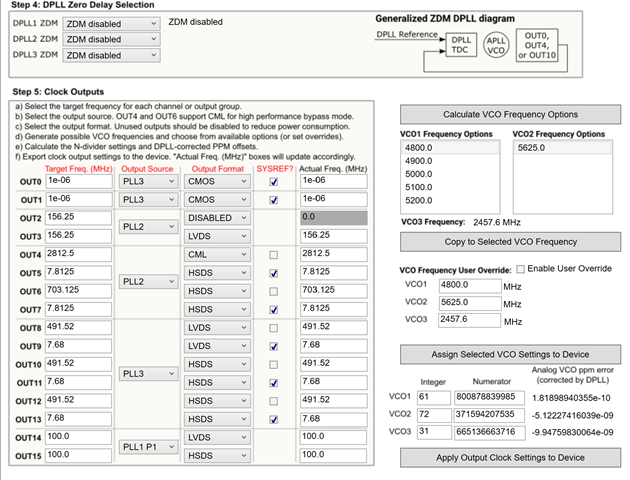

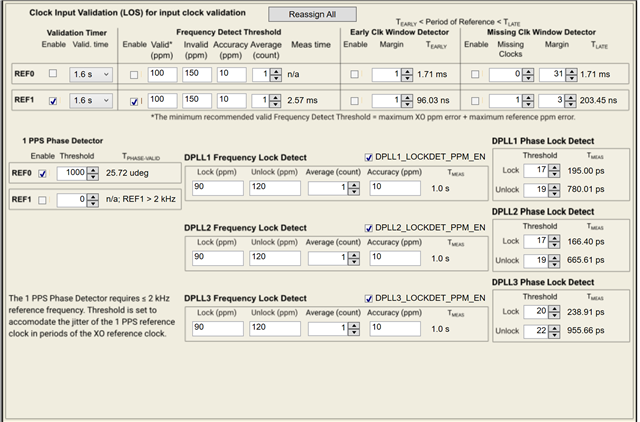

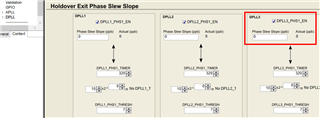

Could you help share the configuration register HexRegisterValues.txt for the 1-PPS input? The development board does not have a default configuration for 1-PPS and ZDM, which is less described in DS and is relatively difficult to use. The customer has tried 1-PPS input from REF0 as reference to DPLL2. DPLL2 ZDM from OUT0 (1 Hz clock signal from SYSREF). There are 3 main issues:

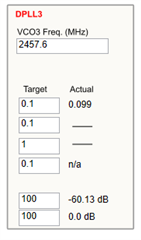

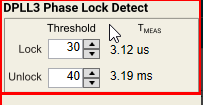

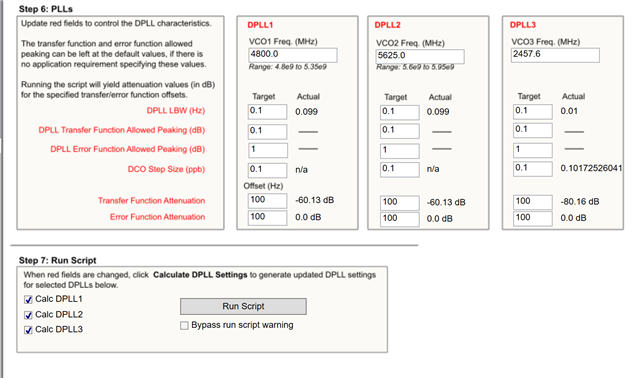

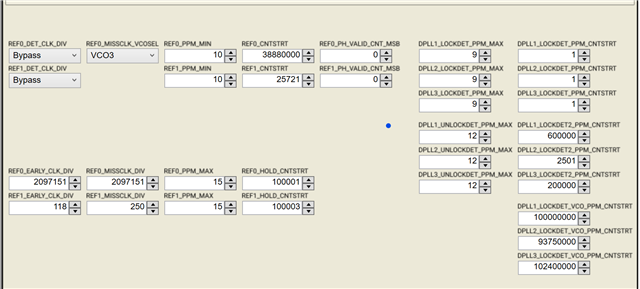

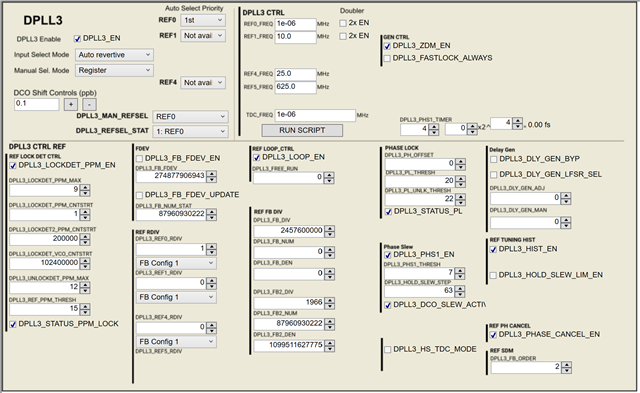

1) Set both DPLL2_REF0_RDIV and DPLL2_FB_DIV to 10, which means that the phasor frequency of the DPLL is 100mHz, but when configured, it was found that APLL2 and DPLL2 were configured with different VCO2 frequencies.

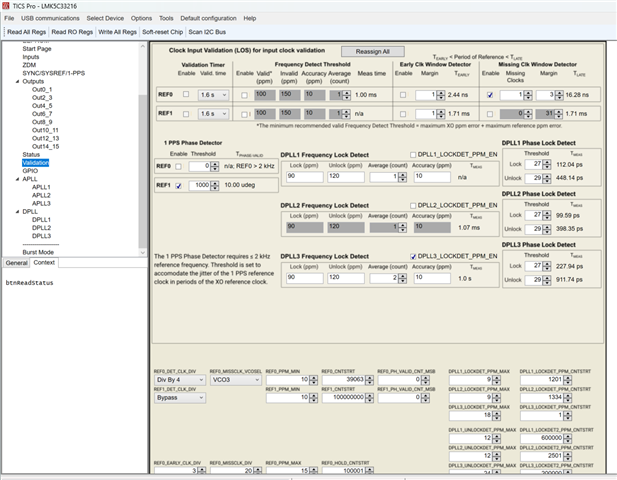

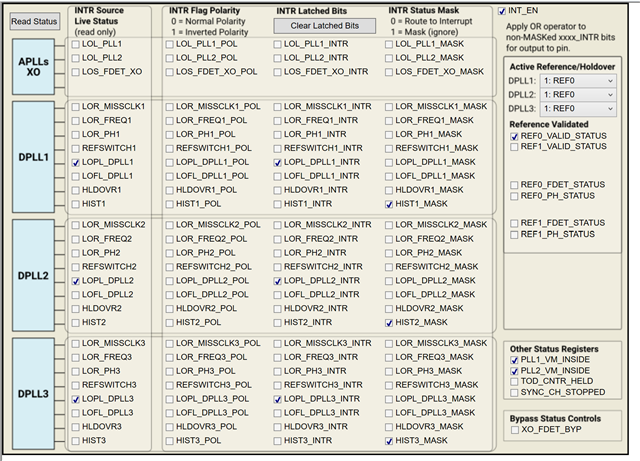

2) How to configure REF0 detection for 1 Hz? Both a 1-Hz square wave and sine wave were tried from REF0, but in the readback state, REF0_VALID_STATUS=0

3) What are the steps to configure the chip for a 1-PPS input?

Could you help check this case? Thanks.

Best Regards,

Cherry