Hi,

I am currently working on the LMX2594PSEVM board and am having problems synchronizing the two PLL's externally.

For testing purpose I use TICS to control the PLL's. To messure the phasedifference between the two Signals I use a VNA (www.rohde-schwarz.com/.../1EZ82).

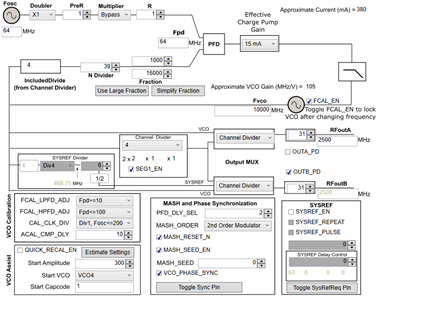

The two PLL's are both locked and working fine. The settings in TICS are as follows:

From the datasheet, I read that these settings fall under SYNC Category 3 for this use case.

But I get a strange behavior, when I send the SYNC pulse multible times (Setup- and Hold-time are above 3ns... so basically okay). Based on my current understanding, the phase relationship of the two output signals should not change when I send the pulse multiple times. However, that is exactly what is happening. In the current settings, there are two angles that (seemingly) change randomly. For example, like this:

1. Pulse: 43°

2. Pulse: 43°

3. Pulse: 36°

4. Pulse: 43°

5. Pulse: 36°

6. Pulse: 36°

...

For my use case, I require a fixed phase relationship of the PLLs after the SYNC.

Did I do something wrong with the TICS settings or did I misunderstand the whole sync feature?

Many thanks

Thomas