Part Number: LMK04826

Hello,

My customer has questions about the LMK04826 SPI interface timing.

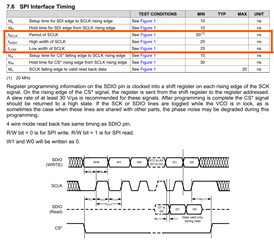

Here is the SPI interface timing table in the LMK04826 datasheet

Q1 ) SCLK's period specification is MIN 50nS(20MHz). When the customer uses 20MHz as SCLK, they are concerned about insufficient margin.

Would there be any problem using 20MHz? Please also explain why.

Q2 ) SCLK's High/Low width specification is MIN 25nS. When the customer uses 20MHz as SCLK, if the High:Low ratio is not 5:5, one side will be less than 25nS. Is this a problem?

Thank you.

JH