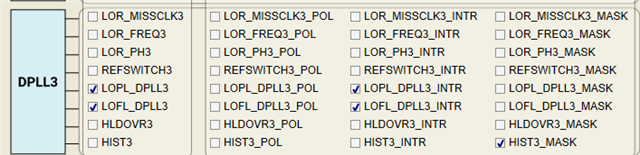

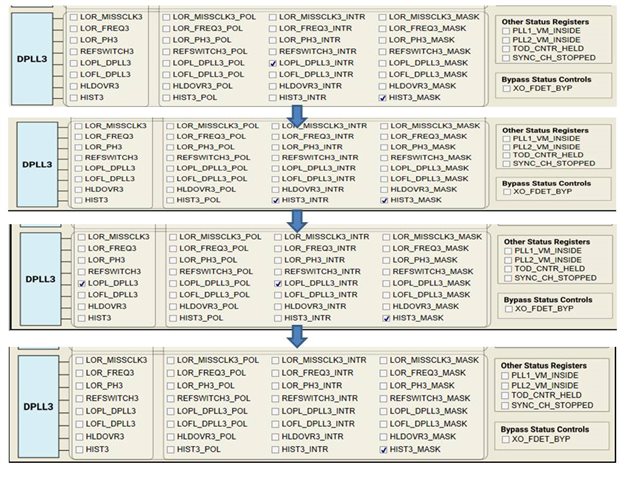

I want to generate a certain clock frequency and in the process, I encountered some issues. I used the attached config files to configure the LMK in TICS Pro. After loading the config file and reading back the status bits, I found that LOPL_DPLL3 is clearing and reappearing randomly when I do "Clear Latched Bits">>"Read Status". I have attached a few instances of the same.

To further verify the phase lock, I tried to find the phase difference between the clock signal generated by the LMK device and the same frequency clock signal generated by a master clock source, which also gives the reference(REF1=10MHz, REF0=100MHz) to the LMK device. It was observed that the phase difference between the two clocks varies with time.

But when the default configuration is used, the phase difference between the LMK clock and master clock is constant wrt time, and also the LOPL_DPLL3 clear on reading the status.

What is the HD2 amplitude that is expected for differential output?