Hello,

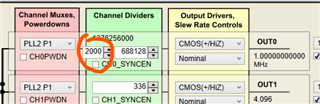

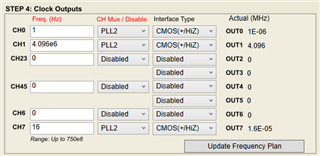

I have issues with LMK05028EVM when configured for a 1PPS reference at the input and 1PPS, 16kHz, and 4.096MHz at the outputs. The clock outputs need to be phase aligned to the output 1PPS clock. As others have noted in this forum, I am having trouble validating the 1PPS reference signal. I also cannot get the DPLL to lock with a valid 1PPS input.

I have tried generating the 1PPS reference from an arbitrary function generator and a Furuno GT-8801 disciplined oscillator. Our product's actual 1PPS clock source will be a Quectel L26T-S89, but this has not been tested. Both tested sources have had reference validation issues when the 1-PPS jitter threshold monitor is enabled (at the maximum value). I can sometimes get the 1PPS to validate using the arbitrary function generator, but it seems very sensitive to voltage, etc.

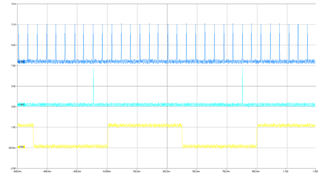

In addition to difficulties getting the reference to validate, I have also been unable to get the DPLL to lock in this configuration. I have tried suggestions made in this forum for this device, but I cannot get the frequency and the phase to lock after a successful reference validation. Below are waveforms of the input 1PPS signal (yellow), output 1PPS signal (cyan), and output 16Hz signal (blue). The outputs are not locked and are not 50% duty for output frequencies of less than about 1200Hz.

The TICS Pro file, which uses the settings from "Run Script" is: MDAQ_LMK05028_1PPS_LO_16HZ.tcs

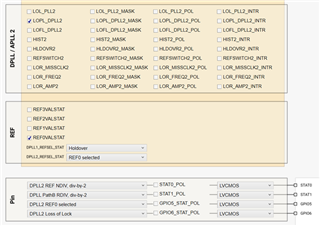

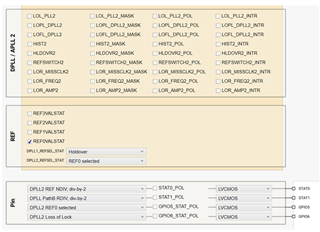

The reference Input Monitors are set as shown below:

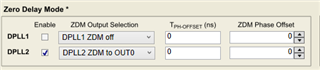

The DPLL lock detectors are configured as shown below:

Thanks.