Other Parts Discussed in Thread: PLLATINUMSIM-SW

Hi team,

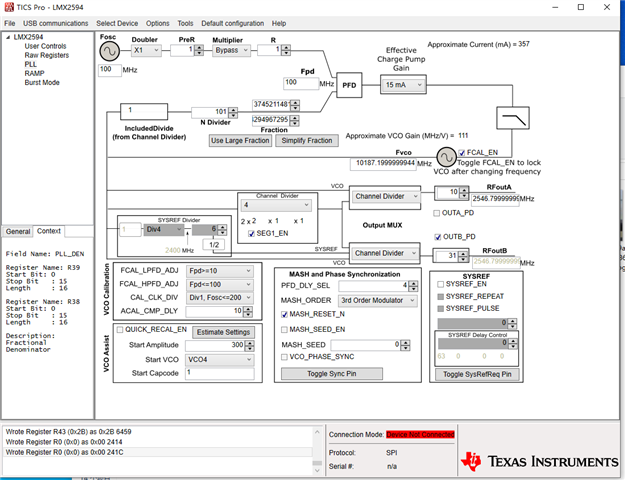

When the denominator is used to its maximum, there are spurs at many frequency points. But some of the frequency points have no spurs. How to avoid fractional spurs by changing the denominator?

Could you help check this case? Thanks.

Best Regards,

Cherry