Part Number: LMK04610

Hi,

I am using lmk04610 on my own pcb. i am trying to configure it with my FPGA Arm core through software with SPI.

I can see that write and read are working great.

what i am trying to do is to lock PLL2. as much as i can see by reading Status0/checking status0 with scope/check register 0xBE, the PLL2 is not lock.

Also i can tell that by looking at the output clock, the clock is not correct, for example if i am trying to get 120MHZ i am getting 111MHZ. checked with differential probes.

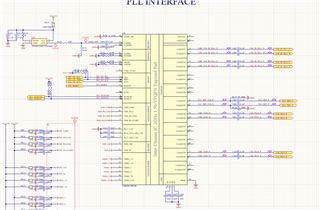

This is my PCB design here:

As you can see, i have 10MHZ input to CLKIN0.

I want only PLL2 because i don't use VCXO, so PLL1 is shutdown.

this is the register i am using:

R0 0x000000 R1 0x000100 R2 0x000200 R3 0x000346 R4 0x000438 R5 0x000503 R6 0x000611 R7 0x000700 R8 0x000800 R9 0x000900 R10 0x000A00 R11 0x000B00 R12 0x000C51 R13 0x000D08 R14 0x000E00 R15 0x000F00 R16 0x00100E R17 0x001100 R18 0x001204 R19 0x001304 R20 0x001400 R21 0x001508 R22 0x001648 R23 0x001700 R24 0x001800 R25 0x001919 R26 0x001A0A R31 0x001F00 R32 0x002001 R33 0x002100 R34 0x002278 R39 0x002714 R40 0x002808 R41 0x002914 R42 0x002A08 R43 0x002B00 R44 0x002C44 R45 0x002D00 R46 0x002E30 R47 0x002F08 R48 0x003001 R49 0x00310C R50 0x003200 R51 0x003300 R52 0x003463 R53 0x003518 R54 0x003603 R55 0x003700 R56 0x003802 R57 0x003918 R58 0x003A03 R59 0x003B00 R60 0x003C02 R61 0x003D00 R62 0x003E63 R63 0x003F00 R64 0x004063 R65 0x004118 R66 0x004203 R67 0x004300 R68 0x00440C R69 0x004500 R70 0x00460C R71 0x004700 R72 0x004808 R73 0x004900 R74 0x004A05 R75 0x004B00 R76 0x004C08 R77 0x004D00 R78 0x004E30 R79 0x004F00 R80 0x005030 R81 0x005100 R82 0x005230 R83 0x005300 R84 0x005430 R85 0x005500 R86 0x005605 R87 0x005718 R88 0x00583F R89 0x005961 R90 0x005A0A R91 0x005B02 R92 0x005C02 R93 0x005D00 R94 0x005E00 R95 0x005F61 R96 0x0060A8 R97 0x006100 R98 0x006278 R99 0x006300 R100 0x006440 R101 0x006500 R102 0x006600 R103 0x006700 R104 0x006800 R105 0x006900 R106 0x006A09 R107 0x006B01 R108 0x006C01 R109 0x006D28 R110 0x006E27 R111 0x006F00 R112 0x007000 R113 0x007100 R114 0x007214 R115 0x007300 R116 0x00741E R117 0x007500 R118 0x007601 R119 0x007701 R120 0x0078FF R121 0x007900 R122 0x007A86 R123 0x007BA0 R124 0x007C08 R125 0x007D00 R126 0x007E00 R127 0x007F34 R128 0x00801F R129 0x008100 R130 0x008200 R131 0x008300 R132 0x00840F R133 0x008501 R134 0x008601 R135 0x008700 R136 0x008840 R137 0x008900 R138 0x008A00 R139 0x008B40 R140 0x008C00 R141 0x008D80 R142 0x008E00 R143 0x008F40 R144 0x009000 R145 0x009100 R146 0x009280 R147 0x009380 R148 0x009404 R149 0x009502 R150 0x009610 R151 0x009720 R152 0x009820 R153 0x009980 R155 0x009B00 R156 0x009C20 R171 0x00AB00 R172 0x00AC00 R173 0x00AD00 R175 0x00AF00 R176 0x00B001 R190 0x00BE03 R246 0x00F600 R247 0x00F700 R249 0x00F907 R250 0x00FAD7 R252 0x00FC00 R253 0x00FD00 R254 0x00FE00 R255 0x00FF00 R256 0x010000 R257 0x010100 R258 0x010200 R259 0x010300 R260 0x010400 R261 0x010500 R262 0x010600 R263 0x010700 R264 0x010800 R265 0x010900 R266 0x010A00 R267 0x010B00 R269 0x010D00 R270 0x010E00 R272 0x011000 R273 0x011100 R274 0x011200 R277 0x011500 R278 0x011600 R279 0x011700 R281 0x011900 R282 0x011A00 R292 0x012408 R295 0x012704 R296 0x012801 R297 0x012905 R298 0x012A01 R299 0x012B04 R300 0x012C05 R301 0x012D04 R302 0x012E01 R304 0x013005 R305 0x013105 R307 0x013305 R308 0x013405 R309 0x013505 R312 0x013805 R313 0x013905 R314 0x013A05 R316 0x013C05 R317 0x013D05 R320 0x01400A R321 0x014109 R322 0x014240 R323 0x014300 R325 0x014500 R326 0x01466C R329 0x014900 R330 0x014A00 R331 0x014B00 R332 0x014C00 R334 0x014E00 R336 0x015000 R337 0x015107 R338 0x015207 R339 0x015307

this is my C code that config these registers:

quick explanation:

1. reset the pll with external RESETn

2. reset the pll with writing register 0x0 the value 0x81 and after 1ms writing 0x00

3. setting register 0x11, 0x85,0x86 to 0x00 AND register 0xF6 to 0x02, as the datasheet said

4. writing registers 0 to the end in ascending order.

5. write register 0xF6 again with value of 0x02

6. write register 0x85 with 0x00

7. write 0x86 with 0x00

8. write 0x11 with 0x01

9. write 0xAD with 0x30

10. wait 20ms

11. write AD with 0x00

12. reading STATUS0 from FPGA input and Also Register 0xBE and also checked with scope - STATUS 0 is not '1'. also i can tell that the PLL2 is not locked!

this order is by the DATASheet guide. where did i wrong?!

st_data_to_spi_u38.splitter_init[0] = 0x000000; //R0

st_data_to_spi_u38.splitter_init[1] = 0x000100; //R1

st_data_to_spi_u38.splitter_init[2] = 0x000200; //R2

st_data_to_spi_u38.splitter_init[3] = 0x000346; //R3

st_data_to_spi_u38.splitter_init[4] = 0x000438; //R4

st_data_to_spi_u38.splitter_init[5] = 0x000503; //R5

st_data_to_spi_u38.splitter_init[6] = 0x000611; //R6

st_data_to_spi_u38.splitter_init[7] = 0x000700; //R7

st_data_to_spi_u38.splitter_init[8] = 0x000800; //R8

st_data_to_spi_u38.splitter_init[9] = 0x000900; //R9

st_data_to_spi_u38.splitter_init[10] = 0x000A00; //R10

st_data_to_spi_u38.splitter_init[11] = 0x000B00; //R11

st_data_to_spi_u38.splitter_init[12] = 0x000C51; //R12

st_data_to_spi_u38.splitter_init[13] = 0x000D08; //R13

st_data_to_spi_u38.splitter_init[14] = 0x000E00; //R14

st_data_to_spi_u38.splitter_init[15] = 0x000F00; //R15

st_data_to_spi_u38.splitter_init[16] = 0x00100E; //R16

st_data_to_spi_u38.splitter_init[17] = 0x001100; //R17

st_data_to_spi_u38.splitter_init[18] = 0x001204; //R18

st_data_to_spi_u38.splitter_init[19] = 0x001304; //R19

st_data_to_spi_u38.splitter_init[20] = 0x001400; //R20

st_data_to_spi_u38.splitter_init[21] = 0x001508; //R21

st_data_to_spi_u38.splitter_init[22] = 0x001648; //R22

st_data_to_spi_u38.splitter_init[23] = 0x001700; //R23

st_data_to_spi_u38.splitter_init[24] = 0x001800; //R24

st_data_to_spi_u38.splitter_init[25] = 0x001919; //R25

st_data_to_spi_u38.splitter_init[26] = 0x001A0A; //R26

st_data_to_spi_u38.splitter_init[27] = 0x001F00; //R31

st_data_to_spi_u38.splitter_init[28] = 0x002001; //R32

st_data_to_spi_u38.splitter_init[29] = 0x002100; //R33

st_data_to_spi_u38.splitter_init[30] = 0x002278; //R34

st_data_to_spi_u38.splitter_init[31] = 0x002714; //R39

st_data_to_spi_u38.splitter_init[32] = 0x002808; //R40

st_data_to_spi_u38.splitter_init[33] = 0x002914; //R41

st_data_to_spi_u38.splitter_init[34] = 0x002A08; //R42

st_data_to_spi_u38.splitter_init[35] = 0x002B00; //R43

st_data_to_spi_u38.splitter_init[36] = 0x002C44; //R44

st_data_to_spi_u38.splitter_init[37] = 0x002D00; //R45

st_data_to_spi_u38.splitter_init[38] = 0x002E30; //R46

st_data_to_spi_u38.splitter_init[39] = 0x002F08; //R47

st_data_to_spi_u38.splitter_init[40] = 0x003001; //R48

st_data_to_spi_u38.splitter_init[41] = 0x00310C; //R49

st_data_to_spi_u38.splitter_init[42] = 0x003200; //R50

st_data_to_spi_u38.splitter_init[43] = 0x003300; //R51

st_data_to_spi_u38.splitter_init[44] = 0x003463; //R52

st_data_to_spi_u38.splitter_init[45] = 0x003518; //R53

st_data_to_spi_u38.splitter_init[46] = 0x003603; //R54

st_data_to_spi_u38.splitter_init[47] = 0x003700; //R55

st_data_to_spi_u38.splitter_init[48] = 0x003802; //R56

st_data_to_spi_u38.splitter_init[49] = 0x003918; //R57

st_data_to_spi_u38.splitter_init[50] = 0x003A03; //R58

st_data_to_spi_u38.splitter_init[51] = 0x003B00; //R59

st_data_to_spi_u38.splitter_init[52] = 0x003C02; //R60

st_data_to_spi_u38.splitter_init[53] = 0x003D00; //R61

st_data_to_spi_u38.splitter_init[54] = 0x003E63; //R62

st_data_to_spi_u38.splitter_init[55] = 0x003F00; //R63

st_data_to_spi_u38.splitter_init[56] = 0x004063; //R64

st_data_to_spi_u38.splitter_init[57] = 0x004118; //R65

st_data_to_spi_u38.splitter_init[58] = 0x004203; //R66

st_data_to_spi_u38.splitter_init[59] = 0x004300; //R67

st_data_to_spi_u38.splitter_init[60] = 0x00440C; //R68

st_data_to_spi_u38.splitter_init[61] = 0x004500; //R69

st_data_to_spi_u38.splitter_init[62] = 0x00460C; //R70

st_data_to_spi_u38.splitter_init[63] = 0x004700; //R71

st_data_to_spi_u38.splitter_init[64] = 0x004808; //R72

st_data_to_spi_u38.splitter_init[65] = 0x004900; //R73

st_data_to_spi_u38.splitter_init[66] = 0x004A05; //R74

st_data_to_spi_u38.splitter_init[67] = 0x004B00; //R75

st_data_to_spi_u38.splitter_init[68] = 0x004C08; //R76

st_data_to_spi_u38.splitter_init[69] = 0x004D00; //R77

st_data_to_spi_u38.splitter_init[70] = 0x004E30; //R78

st_data_to_spi_u38.splitter_init[71] = 0x004F00; //R79

st_data_to_spi_u38.splitter_init[72] = 0x005030; //R80

st_data_to_spi_u38.splitter_init[73] = 0x005100; //R81

st_data_to_spi_u38.splitter_init[74] = 0x005230; //R82

st_data_to_spi_u38.splitter_init[75] = 0x005300; //R83

st_data_to_spi_u38.splitter_init[76] = 0x005430; //R84

st_data_to_spi_u38.splitter_init[77] = 0x005500; //R85

st_data_to_spi_u38.splitter_init[78] = 0x005605; //R86

st_data_to_spi_u38.splitter_init[79] = 0x005700; //R87

st_data_to_spi_u38.splitter_init[80] = 0x00583F; //R88

st_data_to_spi_u38.splitter_init[81] = 0x005961; //R89

st_data_to_spi_u38.splitter_init[82] = 0x005A0A; //R90

st_data_to_spi_u38.splitter_init[83] = 0x005B02; //R91

st_data_to_spi_u38.splitter_init[84] = 0x005C02; //R92

st_data_to_spi_u38.splitter_init[85] = 0x005D00; //R93

st_data_to_spi_u38.splitter_init[86] = 0x005E00; //R94

st_data_to_spi_u38.splitter_init[87] = 0x005F61; //R95

st_data_to_spi_u38.splitter_init[88] = 0x0060A8; //R96

st_data_to_spi_u38.splitter_init[89] = 0x006100; //R97

st_data_to_spi_u38.splitter_init[90] = 0x006278; //R98

st_data_to_spi_u38.splitter_init[91] = 0x006300; //R99

st_data_to_spi_u38.splitter_init[92] = 0x006440; //R100

st_data_to_spi_u38.splitter_init[93] = 0x006500; //R101

st_data_to_spi_u38.splitter_init[94] = 0x006600; //R102

st_data_to_spi_u38.splitter_init[95] = 0x006700; //R103

st_data_to_spi_u38.splitter_init[96] = 0x006800; //R104

st_data_to_spi_u38.splitter_init[97] = 0x006900; //R105

st_data_to_spi_u38.splitter_init[98] = 0x006A09; //R106

st_data_to_spi_u38.splitter_init[99] = 0x006B01; //R107

st_data_to_spi_u38.splitter_init[100] = 0x006C01; //R108

st_data_to_spi_u38.splitter_init[101] = 0x006D28; //R109

st_data_to_spi_u38.splitter_init[102] = 0x006E27; //R110

st_data_to_spi_u38.splitter_init[103] = 0x006F00; //R111

st_data_to_spi_u38.splitter_init[104] = 0x007000; //R112

st_data_to_spi_u38.splitter_init[105] = 0x007100; //R113

st_data_to_spi_u38.splitter_init[106] = 0x007214; //R114

st_data_to_spi_u38.splitter_init[107] = 0x007300; //R115

st_data_to_spi_u38.splitter_init[108] = 0x00741E; //R116

st_data_to_spi_u38.splitter_init[109] = 0x007500; //R117

st_data_to_spi_u38.splitter_init[110] = 0x007601; //R118

st_data_to_spi_u38.splitter_init[111] = 0x007701; //R119

st_data_to_spi_u38.splitter_init[112] = 0x0078FF; //R120

st_data_to_spi_u38.splitter_init[113] = 0x007900; //R121

st_data_to_spi_u38.splitter_init[114] = 0x007A86; //R122

st_data_to_spi_u38.splitter_init[115] = 0x007BA0; //R123

st_data_to_spi_u38.splitter_init[116] = 0x007C08; //R124

st_data_to_spi_u38.splitter_init[117] = 0x007D00; //R125

st_data_to_spi_u38.splitter_init[118] = 0x007E00; //R126

st_data_to_spi_u38.splitter_init[119] = 0x007F34; //R127

st_data_to_spi_u38.splitter_init[120] = 0x00801F; //R128

st_data_to_spi_u38.splitter_init[121] = 0x008100; //R129

st_data_to_spi_u38.splitter_init[122] = 0x008200; //R130

st_data_to_spi_u38.splitter_init[123] = 0x008300; //R131

st_data_to_spi_u38.splitter_init[124] = 0x00840F; //R132

st_data_to_spi_u38.splitter_init[125] = 0x008501; //R133

st_data_to_spi_u38.splitter_init[126] = 0x008601; //R134

st_data_to_spi_u38.splitter_init[127] = 0x008700; //R135

st_data_to_spi_u38.splitter_init[128] = 0x008840; //R136

st_data_to_spi_u38.splitter_init[129] = 0x008900; //R137

st_data_to_spi_u38.splitter_init[130] = 0x008A00; //R138

st_data_to_spi_u38.splitter_init[131] = 0x008B40; //R139

st_data_to_spi_u38.splitter_init[132] = 0x008C00; //R140

st_data_to_spi_u38.splitter_init[133] = 0x008D80; //R141

st_data_to_spi_u38.splitter_init[134] = 0x008E00; //R142

st_data_to_spi_u38.splitter_init[135] = 0x008F40; //R143

st_data_to_spi_u38.splitter_init[136] = 0x009000; //R144

st_data_to_spi_u38.splitter_init[137] = 0x009100; //R145

st_data_to_spi_u38.splitter_init[138] = 0x009280; //R146

st_data_to_spi_u38.splitter_init[139] = 0x009380; //R147

st_data_to_spi_u38.splitter_init[140] = 0x009404; //R148

st_data_to_spi_u38.splitter_init[141] = 0x009502; //R149

st_data_to_spi_u38.splitter_init[142] = 0x009610; //R150

st_data_to_spi_u38.splitter_init[143] = 0x009720; //R151

st_data_to_spi_u38.splitter_init[144] = 0x009820; //R152

st_data_to_spi_u38.splitter_init[145] = 0x009980; //R153

st_data_to_spi_u38.splitter_init[146] = 0x009B00; //R155

st_data_to_spi_u38.splitter_init[147] = 0x009C20; //R156

st_data_to_spi_u38.splitter_init[148] = 0x00AB00; //R171

st_data_to_spi_u38.splitter_init[149] = 0x00AC00; //R172

st_data_to_spi_u38.splitter_init[150] = 0x00AD00; //R173

st_data_to_spi_u38.splitter_init[151] = 0x00AF00; //R175

st_data_to_spi_u38.splitter_init[152] = 0x00B001; //R176

st_data_to_spi_u38.splitter_init[153] = 0x00BE03; //R190

st_data_to_spi_u38.splitter_init[154] = 0x00F600; //R246

st_data_to_spi_u38.splitter_init[155] = 0x00F700; //R247

st_data_to_spi_u38.splitter_init[156] = 0x00F907; //R249

st_data_to_spi_u38.splitter_init[157] = 0x00FAD7; //R250

st_data_to_spi_u38.splitter_init[158] = 0x00FC00; //R252

st_data_to_spi_u38.splitter_init[159] = 0x00FD00; //R253

st_data_to_spi_u38.splitter_init[160] = 0x00FE00; //R254

st_data_to_spi_u38.splitter_init[161] = 0x00FF00; //R255

st_data_to_spi_u38.splitter_init[162] = 0x010000; //R256

st_data_to_spi_u38.splitter_init[163] = 0x010100; //R257

st_data_to_spi_u38.splitter_init[164] = 0x010200; //R258

st_data_to_spi_u38.splitter_init[165] = 0x010300; //R259

st_data_to_spi_u38.splitter_init[166] = 0x010400; //R260

st_data_to_spi_u38.splitter_init[167] = 0x010500; //R261

st_data_to_spi_u38.splitter_init[168] = 0x010600; //R262

st_data_to_spi_u38.splitter_init[169] = 0x010700; //R263

st_data_to_spi_u38.splitter_init[170] = 0x010800; //R264

st_data_to_spi_u38.splitter_init[171] = 0x010900; //R265

st_data_to_spi_u38.splitter_init[172] = 0x010A00; //R266

st_data_to_spi_u38.splitter_init[173] = 0x010B00; //R267

st_data_to_spi_u38.splitter_init[174] = 0x010D00; //R269

st_data_to_spi_u38.splitter_init[175] = 0x010E00; //R270

st_data_to_spi_u38.splitter_init[176] = 0x011000; //R272

st_data_to_spi_u38.splitter_init[177] = 0x011100; //R273

st_data_to_spi_u38.splitter_init[178] = 0x011200; //R274

st_data_to_spi_u38.splitter_init[179] = 0x011500; //R277

st_data_to_spi_u38.splitter_init[180] = 0x011600; //R278

st_data_to_spi_u38.splitter_init[181] = 0x011700; //R279

st_data_to_spi_u38.splitter_init[182] = 0x011900; //R281

st_data_to_spi_u38.splitter_init[183] = 0x011A00; //R282

st_data_to_spi_u38.splitter_init[184] = 0x012408; //R292

st_data_to_spi_u38.splitter_init[185] = 0x012704; //R295

st_data_to_spi_u38.splitter_init[186] = 0x012801; //R296

st_data_to_spi_u38.splitter_init[187] = 0x012905; //R297

st_data_to_spi_u38.splitter_init[188] = 0x012A01; //R298

st_data_to_spi_u38.splitter_init[189] = 0x012B04; //R299

st_data_to_spi_u38.splitter_init[190] = 0x012C05; //R300

st_data_to_spi_u38.splitter_init[191] = 0x012D04; //R301

st_data_to_spi_u38.splitter_init[192] = 0x012E01; //R302

st_data_to_spi_u38.splitter_init[193] = 0x013005; //R304

st_data_to_spi_u38.splitter_init[194] = 0x013105; //R305

st_data_to_spi_u38.splitter_init[195] = 0x013305; //R307

st_data_to_spi_u38.splitter_init[196] = 0x013405; //R308

st_data_to_spi_u38.splitter_init[197] = 0x013505; //R309

st_data_to_spi_u38.splitter_init[198] = 0x013805; //R312

st_data_to_spi_u38.splitter_init[199] = 0x013905; //R313

st_data_to_spi_u38.splitter_init[200] = 0x013A05; //R314

st_data_to_spi_u38.splitter_init[201] = 0x013C05; //R316

st_data_to_spi_u38.splitter_init[202] = 0x013D05; //R317

st_data_to_spi_u38.splitter_init[203] = 0x01400A; //R320

st_data_to_spi_u38.splitter_init[204] = 0x014109; //R321

st_data_to_spi_u38.splitter_init[205] = 0x014240; //R322

st_data_to_spi_u38.splitter_init[206] = 0x014300; //R323

st_data_to_spi_u38.splitter_init[207] = 0x014500; //R325

st_data_to_spi_u38.splitter_init[208] = 0x01466C; //R326

st_data_to_spi_u38.splitter_init[209] = 0x014900; //R329

st_data_to_spi_u38.splitter_init[210] = 0x014A00; //R330

st_data_to_spi_u38.splitter_init[211] = 0x014B00; //R331

st_data_to_spi_u38.splitter_init[212] = 0x014C00; //R332

st_data_to_spi_u38.splitter_init[213] = 0x014E00; //R334

st_data_to_spi_u38.splitter_init[214] = 0x015000; //R336

st_data_to_spi_u38.splitter_init[215] = 0x015107; //R337

st_data_to_spi_u38.splitter_init[216] = 0x015207; //R338

st_data_to_spi_u38.splitter_init[217] = 0x015307; //R339

u16 addr = 0x0;

u32 data1;

//init spi

Init_lmk04610_spi();

////////Recommended Programming Sequence for LMK04610//////

// The default programming sequence from POR involves:

// 1. Toggle RESETn pin High-Low-High

// 2. Program all registers with Register 0x0011 bit 0 = 0 //STARTUP

// -Register 0x85 = 0x00 //PLL2_LD_WNDW_SIZE[7:0]

// -Register 0x86 = 0x00 //PLL2_LD_WNDW_SIZE_INITIAL

// -Register 0xF6 = 0x02 //PLL2_DLD_EN

// 3. Program Register 0x0011 bit 0 = 1 to start the device //STARTUP

// 4. Enable PLL2 digital lock detect

// -0xAD = 0x30 //PLL2_CTRL

// -Delay 20 ms

// -0xAD = 0x00 //PLL2_CTRL

DeviceConfiguration.ControlBits.PLL_RESET = 1;

Xil_Out32(FPGA_CONTROL_ADDR, DeviceConfiguration.Control);

usleep(1000);

DeviceConfiguration.ControlBits.PLL_RESET = 0;

Xil_Out32(FPGA_CONTROL_ADDR, DeviceConfiguration.Control);

usleep(1000);

DeviceConfiguration.ControlBits.PLL_RESET = 1;

Xil_Out32(FPGA_CONTROL_ADDR, DeviceConfiguration.Control);

sleep(1);

//reset the chip

st_data_to_spi_u38.splitter_init[0]=0x000081;

lmkWriteReg(st_data_to_spi_u38.splitter_init[0]>>8, st_data_to_spi_u38.splitter_init[0]);

usleep(1000);

//release reset the chip

st_data_to_spi_u38.splitter_init[0]=0x000000;

lmkWriteReg(st_data_to_spi_u38.splitter_init[0]>>8, st_data_to_spi_u38.splitter_init[0]);

sleep(1);

st_data_to_spi_u38.splitter_init[17] = 0x001100; //R17 0x11 //STARTUP

st_data_to_spi_u38.splitter_init[125] = 0x008500; //R133 0x85 //PLL2_LD_WNDW_SIZE[7:0]

st_data_to_spi_u38.splitter_init[126] = 0x008600; //R134 0x86 //PLL2_LD_WNDW_SIZE_INITIAL

st_data_to_spi_u38.splitter_init[154] = 0x00F602; //R246 0xF6 //PLL2_DLD_EN

for (write_no = 0; write_no <= 217 ; write_no++) {

lmkWriteReg(st_data_to_spi_u38.splitter_init[write_no]>>8, st_data_to_spi_u38.splitter_init[write_no]);

usleep(100);

}

usleep(10000); //5

st_data_to_spi_u38.splitter_init[154] = 0x00F602; //R154 0xF6

lmkWriteReg(st_data_to_spi_u38.splitter_init[154]>>8, st_data_to_spi_u38.splitter_init[154]);

usleep(10000);

st_data_to_spi_u38.splitter_init[125] = 0x008500; //R133 0x85 //PLL2_LD_WNDW_SIZE[7:0]

lmkWriteReg(st_data_to_spi_u38.splitter_init[125]>>8, st_data_to_spi_u38.splitter_init[125]);

usleep(10000);

st_data_to_spi_u38.splitter_init[126] = 0x008600; //R134 0x86 //PLL2_LD_WNDW_SIZE_INITIAL

lmkWriteReg(st_data_to_spi_u38.splitter_init[126]>>8, st_data_to_spi_u38.splitter_init[126]);

st_data_to_spi_u38.splitter_init[17] = 0x001101; //R17 0x11 //STARTUP

lmkWriteReg(st_data_to_spi_u38.splitter_init[17]>>8, st_data_to_spi_u38.splitter_init[17]);

sleep(2);

st_data_to_spi_u38.splitter_init[150] = 0x00AD30; //R173

lmkWriteReg(st_data_to_spi_u38.splitter_init[150]>>8, st_data_to_spi_u38.splitter_init[150]);

usleep(20000);

st_data_to_spi_u38.splitter_init[150] = 0x00AD00; //R173

lmkWriteReg(st_data_to_spi_u38.splitter_init[150]>>8, st_data_to_spi_u38.splitter_init[150]);

sleep(1); //wait 3 sec for clock to stabilize

//read status reg

uint32_t status_in = Xil_In32(0x80000000+0x00A4); //

xil_printf("- Successfully run lmk04610 configuration %x \r\n\n",status_in);

xil_printf(" \r\n\n");

addr = st_data_to_spi_u38.splitter_init[153]>>8;

dat = lmkReadReg(addr); // Dummy read

data1 = addr << 8|dat;

xil_printf("st_data_to_spi_u38.splitter_init[%d] = 0x%x;\r\n",write_no,data1);

usleep(100);

thanks

ofer k.