Hi Team,

We use yours component LMX1204 in a custom PCB board. We encountered some difficulties in the SPI Programming signals (SCLK,SDO,SDI & CS).

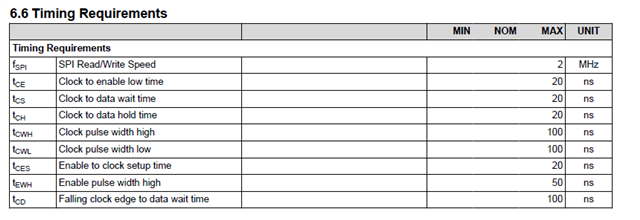

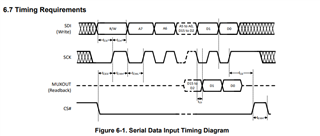

In the Figure 6-1 of the datasheet that is illustrated below, the SPI is defined (also in the text following the figure in the datasheet "Recommended SPI settings for this device are CPOL=0 and CPHA=0.". This means, like the figure below that the first edge of the SCLK after the CS# is a rising edge, and the clock pin when there are no SPI cycles performed is low. Also the Datas on SDI and SDO are sampled on the rising edge of the clock and "changed" on the falling edge.

Since we can't program the LMX1204 on our custom PCB, we perform different analysis and since we have bought also the LMX1204 eval board we measure the SDI,SCLK and CS# on the pins provided on the eval board.

I will show the oscilloscope signals on the board in the figure below.

It seems like the CPOL is not 0 but 1, since the first edge of the SCLK is falling after the CS#. I will zoom it for you:

The yellow plot is the CS, the violet the SCLK and the blue the SDI.

We use the TICS PRO SW interface to program the LMX1204 Eval board.

Can someone explain me why there is this difference between the Datasheet and the operation mode used on the Eval Board?

Thank you very much,

Best regards!