we have a big fracrational calcuation.

the divider is 56.8798076923077

how to achieve such accruacy and also how to reduce the vco relock and calibation time?

thanks

chen

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

we have a big fracrational calcuation.

the divider is 56.8798076923077

how to achieve such accruacy and also how to reduce the vco relock and calibation time?

thanks

chen

Hi Chen,

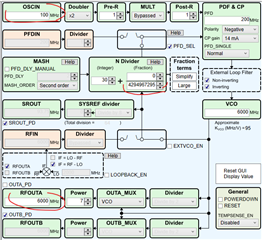

You can use TICS Pro, change the PLL_DEN to the highest value, then input the input and output frequency, the tool will do the calculation for you. However the tool is limited to 10 decimal places, you will need to do some calculation to see how close is the result to your desired frequency.

hello Noel Fung

thanks for helping

we order this boards

but we can not find the instruction on how to connect this board with the pins with stm32.

could you share us how

meanwhile, when we put 26mhz as the oscin, we can not make mult and doubler enable at the same time, this is not seen in the datasheet but only this tics pro tool, how to increase the pdf then?