Part Number: LMK05318

Other Parts Discussed in Thread: LMK5C33216, LMK5B33216

Hi Team,

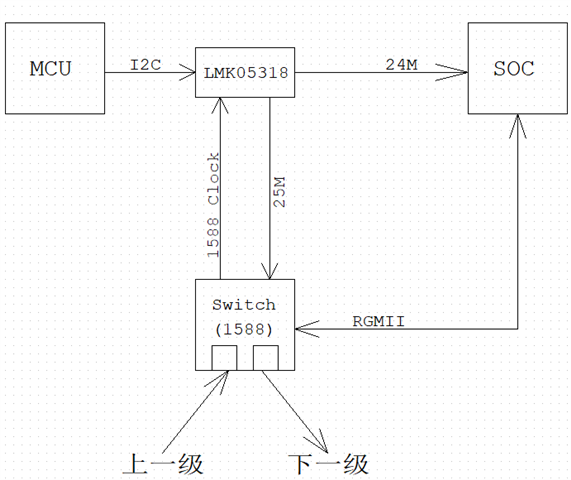

The customer would like to use LMK05318 example for 1588 synchronization scheme and please see the following diagram for details.

The consumer's goal is to synchronize these N devices with 1588.

The switch recovers 1588 clock from the previous stage, output to the reference clock input of the LMK05318, and the two output clocks of the LMK05318 (25M and 24M) are automatically synchronized to 1588 clock (sync frequency and phase), could you help tell if the above understanding correct or not?

1) Can the LMK05318 synchronize frequency lock and phase lock of 1588 clock on the switch output?

2) Is there a special software algorithm to adjust the output synchronization frequency of the LMK05318?

3) Is the above solution feasible? If possible, what is the synchronization accuracy?

Could you help check this case? Thanks.

Best Regards,

Cherry