Other Parts Discussed in Thread: ADC12DJ3200, , ADC12DJ3200EVM,

Hello,

My customer is using LMK04832 to provide main clock and SYSREF clock to ADC12DJ3200.

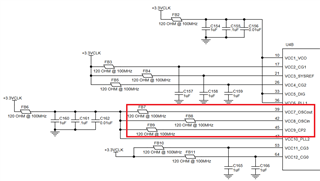

They designed the power inputs of VCC7~9 of the LMK04832 as follows in the same way as the ADC12DJ3200EVM circuit.

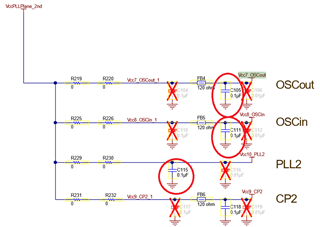

Recently, they found that capacitors were added to the VCC7~9 power input of the LMK04832EVM, unlike the ADC12DJ3200EVM circuit.

Q1) What is the role of the above capacitors?

Q2) Is the use of the above capacitors mandatory?

Q3) Is ADC12DJ3200EVM's LMK048xx circuit wrong? Or did you remove the capacitors for some other purpose?

Thank you.

JH