Other Parts Discussed in Thread: LMK04906, , CODELOADER, USB2ANY

Hi.

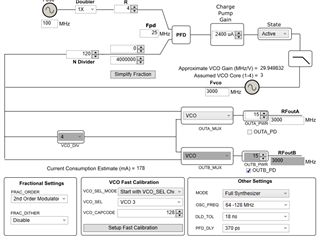

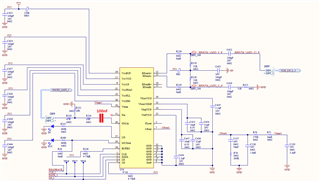

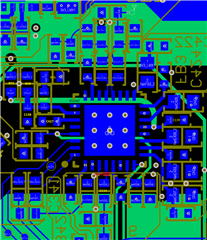

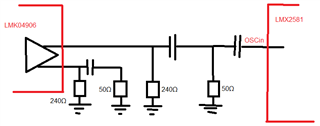

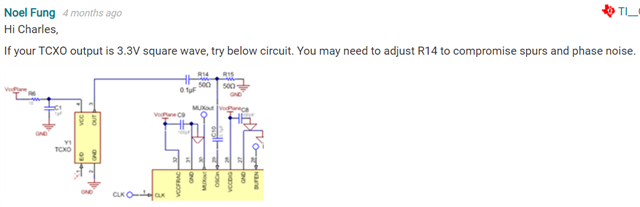

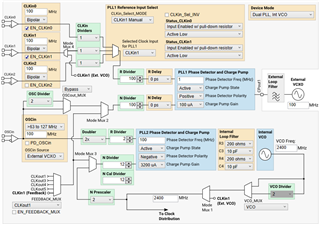

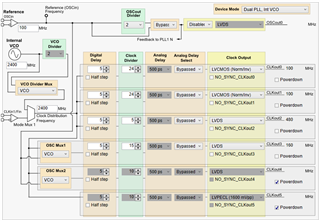

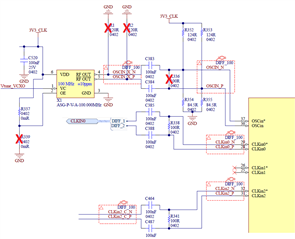

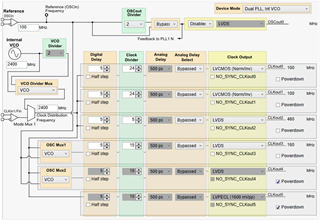

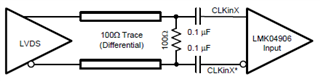

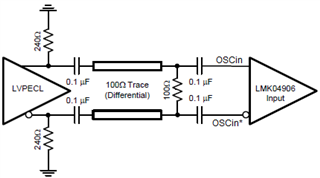

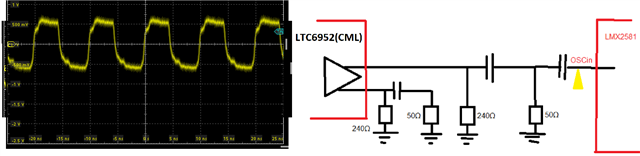

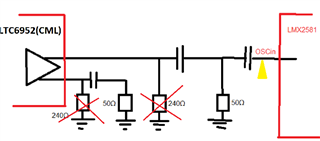

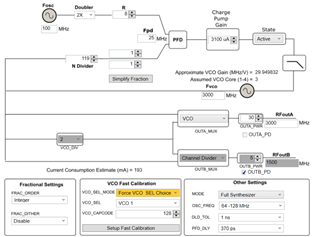

In project we have using two LMX2581 in one PCB, both are the the same circut, role, and very similar layout. On the other hand, layout doesn't differ significantly from EVM board. Both have OSCin signal distributed by LMK04906 with frequency 100MHz, and amplitude about 1,6Vpp (on OSCin pin), is good looking suqare wave. Desing circut, in loop filter section is similar as in 9.2.2.2 chapter in datasheet. Our target is to acheive output frequencies from 1-2GHz (1000G, and 1500G for example), on one output of each chip. We use TICS Pro to generate register values, and write it by SPI using Raspberry Pi. Programing sequence of LMX2581 contain: program R5 with RESET bit, program registers R15-R0 with about 500us delay between each register, and again program R0 after about 160ms. Chips are programmed each time in sequence: LMK, LMX(1), LMX(2), so i can observe beachvior on two LMX because each get the same cofiguration. DIfference is one: LMX(1) has AC-coupling capacitor in OSC signal near the LMK, but LMX(2) has additional capacitor directly before OSCin pin (to do the circut identicaly like EVM board). Clock from LMK04906 is still present, but chips are on the same board.

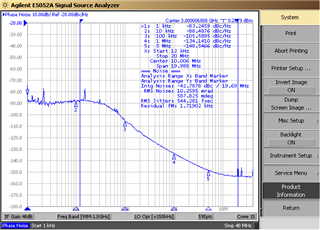

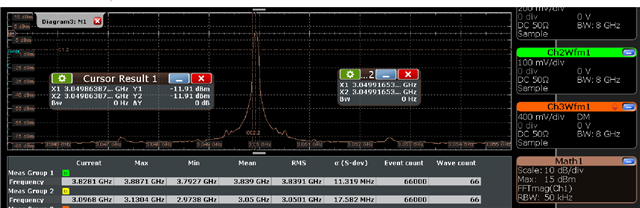

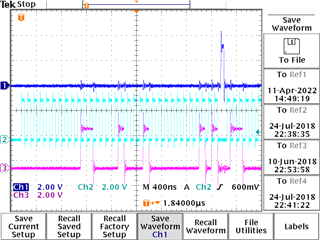

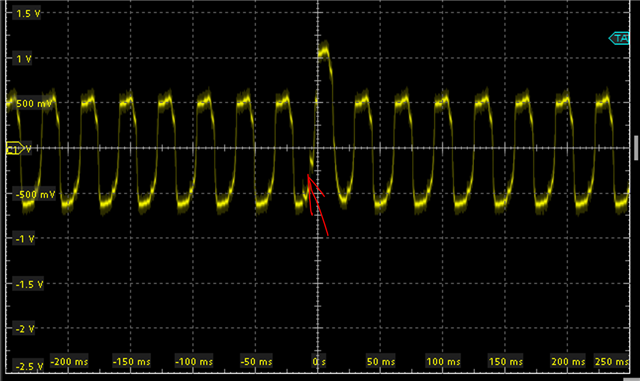

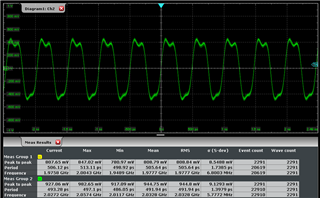

I tried to achaive target output frequencies, but when it get unsuccesfull i tried to get any set frequency and get lock status. I tried several dozen configurations, and can't achaive proper frequency, and get "DLD & Vtune Good" on LD pin. In some cases device gives maximum VCO freqency, eventually divided by VCO_DIV. In other configurations the frequency is wrong, but not like extreme of VCO, and sometimes differs between two programming sequences with the same config. In some configurations device gives frequency differs from config (example: set 1900M, get 2200M, or 2050M), but i get "Vtune" on LD pin (good sign :) ) and Vtune voltage is stable about 1,26V, what mean (as i readed from other topics) that the voltage tuning is OK, and analog part is propoerty locked, but i cant get the "DLD" (Digital Lock Detect). In some configs i get 1810MHz, when set 1805MHz, what looks good, but any lock occurs, deviation is 3MHz, and changing set frequence down to for exampe 1750MHz, i get 1900MHz. Now i put more hope in LMX2581 with additional capacitor on OSCin pin, because it always set the "OSCin Det" on LD, when LMX with no additional capacitor set it sometimes. I tried to: changing VCO (by force), pump gain, dividers and multiplers combinations, VCO_CAPCODE values, Fpd frequency, changing programing sequence (for example adding 3 times programmming R0 and sometimes it changes effects) and some others and cant get it. I see that the highest Fpd frequency is better (as described in datasheet) but not always. I tried to use LD pin as "R/2", or "R/4", but in some cases i did not get this signal on LD pin. Output frequencies has deviations about 1-3MHz. Sometimes i see that the frequency is proper for a fraction of a second after programming, and change to unproper. I have some questions about diagnostic functions, and of course main question:

1. How to get proper frequency and lock? How can i debug, or diagnose it?

2. Can i interpret "OSCin Det" on LD pin as the OSCin signal is proper? Information in datasheet mean that i can't.

3. How can i check that 4 important things was right: programming, input signal, voltage lock, digital lock?

I think is the digital (phase detector) issue, but as i think if the Vtune voltage is proper, we need just phase detection, but i don't know how to diagnose/debug it.

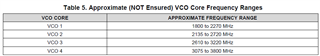

Now i back to starting point (9.2.2.2 chapter config from dataseheet). Set config as below, and get freqency as below ( on LMX2581 with additional capacitor on OSCin pin, because without it, the second LMX gives 2800MHz), "Vtune" high on LD, and Vtune voltege 1,23V.

I would be very grateful for your help.

Best regards