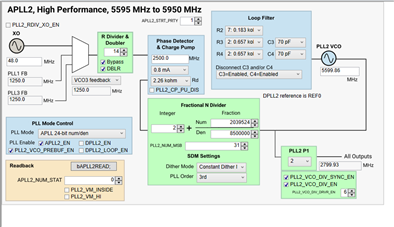

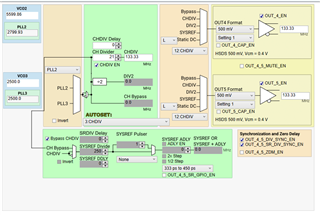

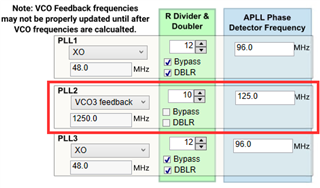

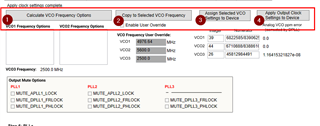

I'm trying to generate a 133.33MHz clock on outputs 4,5,and 6 using an LMK5B33216EVM evaluation board. I have the APLL2 using the BAW as its reference. I have the channel dividers set to 21 and the APPL2 post divider set to 2. The plan is to use an APLL2 frequency of 5599.86MHz and divide the output by 42 to get 133.33MHz.

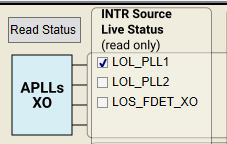

But when I look at the LVDS output of channel 4, I get a frequency of 138.98MHz instead of 133.33MHz. That means that APLL2 is running at 138.98 x 42 = 5837.16MHz instead of 5599.86MHz.

I have tried using an APPL2 frequency of 5600MHz and got the same results. I have also tried using a PLL frequency of 5866.2 and divide by 44. In that case, I get an output frequency of 132.66MHz which implies that the PLL is running at 44x132.66MHz=5837.04MHz instead of 5866.2MHz.

All the clocks that feed of APLL3 work correctly. Here are my configurations. I'm not using the DPLL. I have also attached my TICS PRO configuration if someone wants to look at it.