Hi,

I have a clock jitter issue here.

I used the syncE recover the clock for clock transmission, but when I connected too many devices in series(more than 8), the PHY don't work. After measurement, it was found that as the clock transmit, the jitter increased.

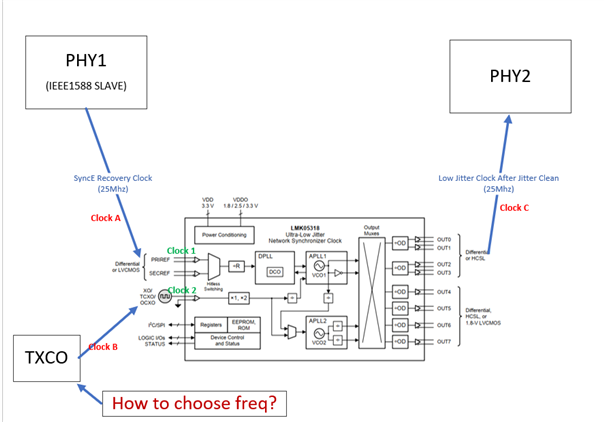

I would like to use LMK05318 as a jitter cleaner chip, as follows:

My recovered clock is 25Mhz,that means, the input of lmk05318 is 25Mhz,and output is 25Mhz.

Here is my question:

1、Does LMK05318 meet my needs for clock jitter clean?

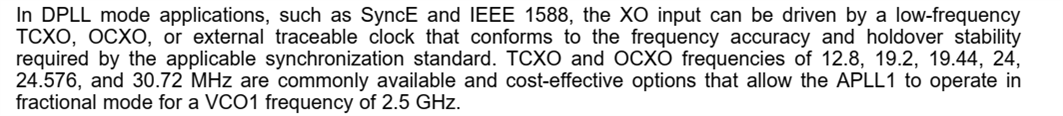

2、the VCXO is needed?

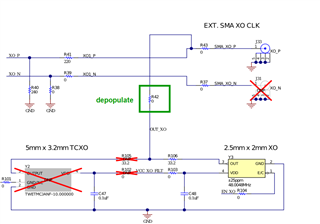

3、Can I complete the testing on the LMK05318 EVM, I found that there is only a 48.0048-MHz XO on board.

Best Regards,

Kevin