Hello,

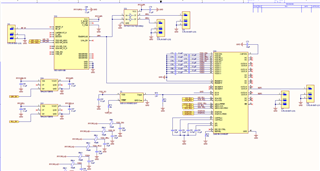

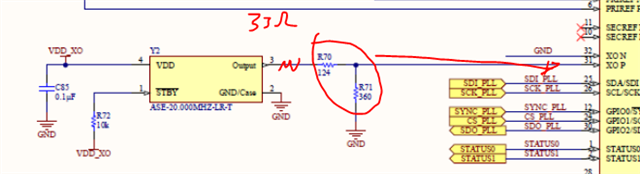

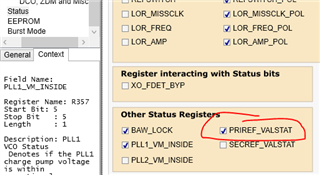

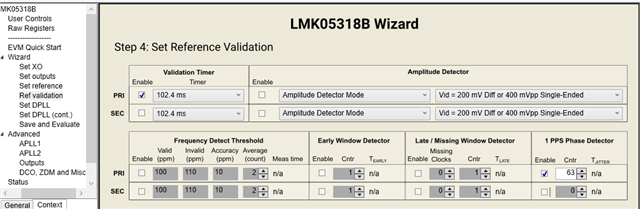

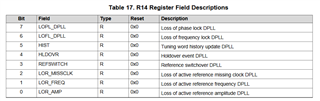

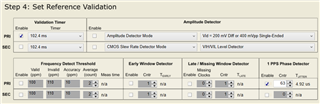

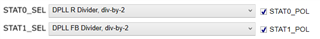

I am using TICSPro to generate the raw registers which I then load into the chip over SPI. This all seems to work fine. I have the STATUS0_SEL set to "DPPL Loss of Lock (LOFL). It is set to high, which means the DPLLis not locked. I have pasted my schematic in case anything seems off. I cannot seem to be able to insert my TICSPro file.

I am able to output a 10MHz tone on out2 and out3, however, it does not seem to be locked to GPS 1PPS. If there's anything that jumps out that is wrong, I would appreciate the help.

Thanks!