Other Parts Discussed in Thread: LMK04832

Hi ,

To understand how the LMK04832 works, we have the evaluation card that Ti offers. (VCXO 122.88 MHz)

I would like to use the LMK04832 in "holdover" mode and I would like a little more explanation on exiting this mode.

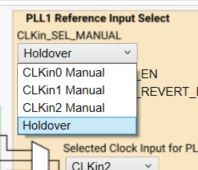

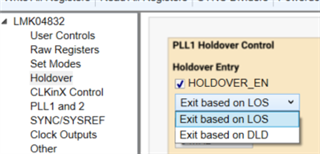

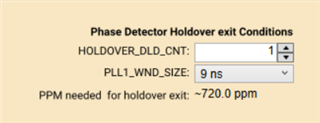

On the "pll1 holdover control" I select an exit mode "exit based on DLD"

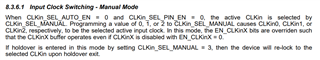

I use an external 10MHz reference clock connected to CLKin1. (CLKin0 is not selected)

This reference clock may or may not be present.

In the absence (10MHz reference clock = OFF) of this clock, the LMK04832 switches to "Holdover" mode with a pre-established DAC voltage (CPout1).

On the other hand, when this reference clock returns, the LMK04832 remains in "holdover" mode, it does not want to lock onto this reference clock.

Can you explain this to me?

Second scenario, can we adjust the entry into "holdover" mode according to the frequency of the external clock.

I observe the operation by varying the frequency of the external reference clock 10MHz+350Hz and 10MHz-520Hz the PLL1 goes off (LD1 off)

The voltage on the VCXO follows the variation of the external clock frequency (the voltage on the VCXO is either 0 or +3.3V in this case).

On the other hand, when the PLL1 comes off I would like the LMK04832 to be able to switch to "holdvover" mode.

Is it possible ?

Attached is the Holdover_mode_exit_based_on_DLD.tcs file

Holdover_mode_exit_based_on_DLD.tcs

Thank you for the help provided.

Best regards

David