Other Parts Discussed in Thread: LMK04832

Hi Team,

The customer is trying to validate the digital and analogue delays for lmk04828.

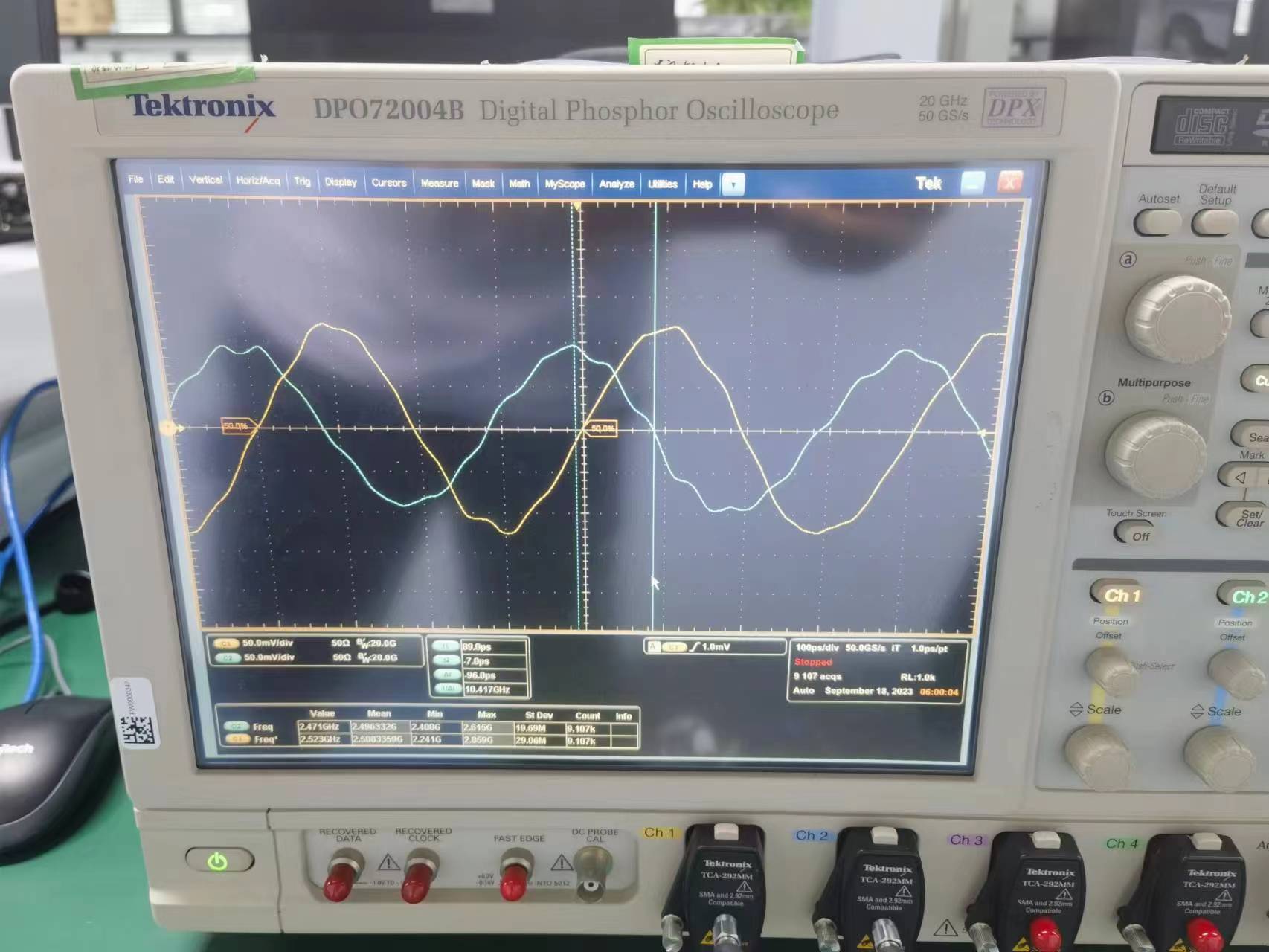

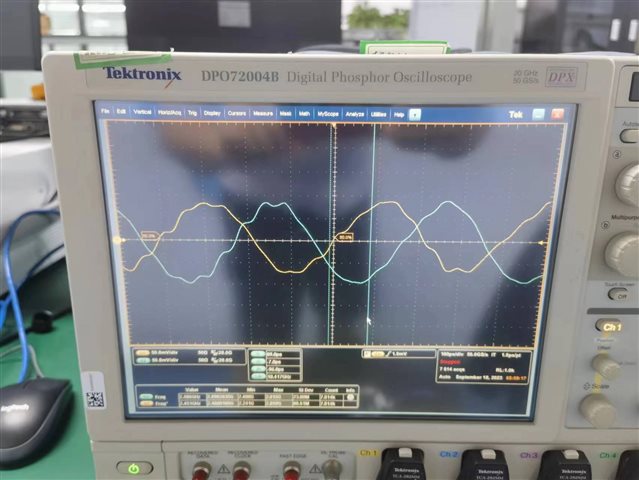

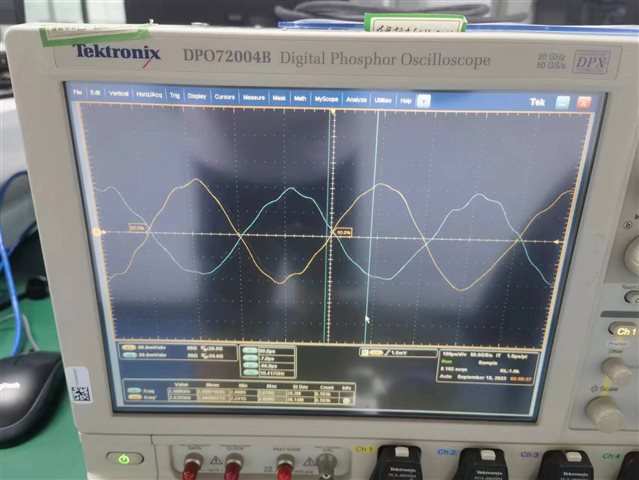

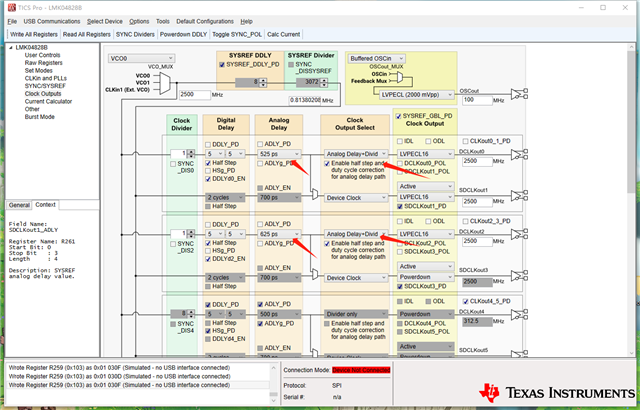

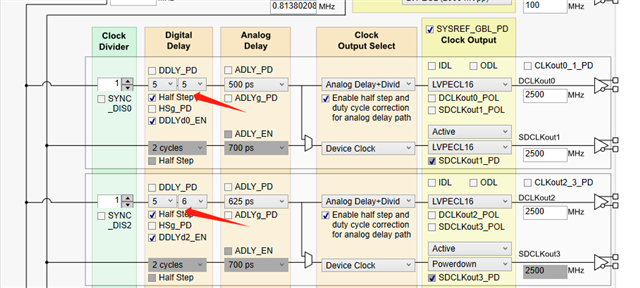

The clkin1 input is a 20 MHz clock and the oscin input is a 100 MHz clock. Vco0 is 2500 MHz. Dclkout0 is 2500 MHz, dclkout2 is 2500 MHz. An oscilloscope is used to test the delay of these two clocks.

Regarding Analogue delay: Set clock output select to analogue delay + divider on TICSPRO. After the chip configuration is complete, change the delay value in analogue delay to see that the clock delay did change, but the changed value and the set value are different.

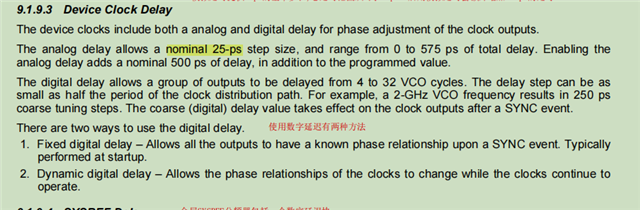

Regarding to the digital delay function, it has two modes according to the manual:

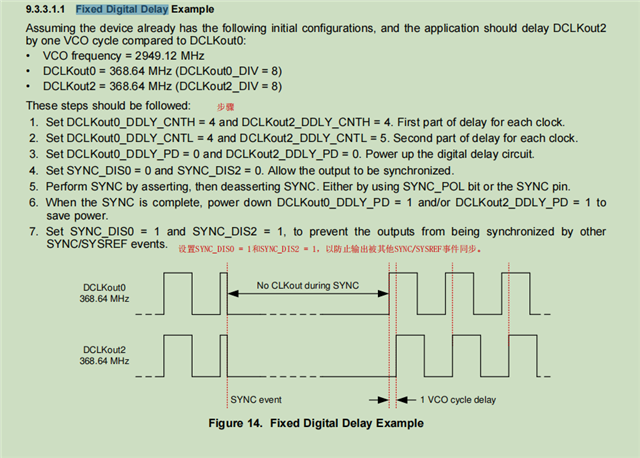

The customer is attempted to use the example on the manual to verify the Fixed Digital delay:

- Set DCLKout0_DDLY_CNTH/L to a value of 4,4;

- Set DCLKout0_DDLY_CNTH/L to a value of 4,5;

- Set DCLKout0_DDLY_PD = 0 and DCLKout2_DDLY_PD = 0;

- Set sync_DIS0 = 0 and sync_DIS2 = 0;

- Then sync_pol write 1 and then 0.

VCO0 is known to be 2500 MHz. The modified delay is half a VCO0 cycle, that is, it should be 200 ps, which means dclkout0 and dclkout1 should be inverted. But the output clock doesn't change in reality.

Could you help look into this case? Thanks.

Best Regards,

Cherry