Hi team,

Customer generate 6GHz CLK with LMK04832 by the below methodology.

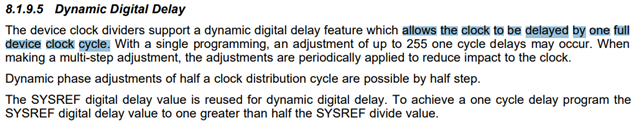

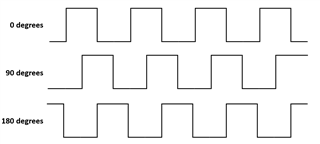

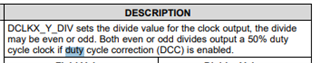

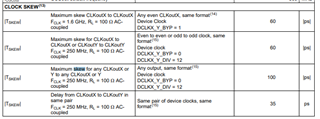

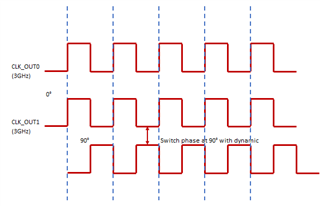

- Shift phase with half CLK against reference CLK.

- Shift phase dynamically between same phase and shifted phase with half CLK.

Regarding the above inquiry, is it possible with LMK04832 Dynamic Digital Delay ?

Thank you and best regards,

Michiaki Tanii