Hi,

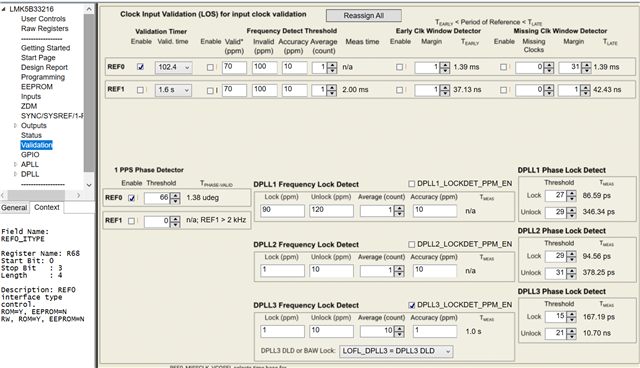

I tried to lock DPLL3 with 1-pps and APLL3 with TCXO of 48MHz for the output of 156.25MHz at output port 4. The PDF I use was 32MHz. I was not able able to get the LMK5B33216 to consistently 1-pps phase lock using the 48 MHz TCXO. There are periods of time where it does lock, but this is intermittent and does not stay locked, even after waiting up to 60 mins. Weeks ago, I got a support for a 100MHz TCXO case (with PDF of 66.6666MHz) which result in phase lock after 10 minutes but running at 48 MHz takes at least 20 minutes to lock. Is there any setting that I can do with solid lock as well as shortening the lock time? FYI, here is the validation page I used. The validation DPLL3 Phase Lock Detect does not seem to save the new number that I entered when recalled. I had to re-enter the new value whenever I recall the state file. Do you have any idea for it?

The way I watch the Lock status was monitoring the three LEDs on the board. Please see attached picture, red rectangular area. By setting up GPIO1 as LOPL_DPLL3 at the GUI, I believe the middle LED turns off, once DPLL3 is locked. At locking process the middle LED is lit on solid while the left and right LEDs blinks alternatively. Once locked, the middle LED turns off. I believe that means it was locked. about 30-45 min. later, I found the middle LED turned on again with both left and right LEDs blinks simultaneously. ?I think it lost the lock status. Let me know if there is anything missing here or to try something out.

If you can provide a state file for the use case of 1-pps lock with 48MHz TCXO in a solid way and fast way, that would be really great.

Thanks,