Part Number: CDCE6214

Hi team,

Customer would like to change the clock frequency with as little dead time as possible. They would like the CDCE6214 to behave in the following way:

Frequency 1 – Output muted – Frequency 2

1: What is the fastest way to mute and unmute an output? In the datasheet it says you can appoint a GPIO to the OUTPUT enable function, but it takes 4 clock cycles for the output to be actually muted, and 4 clock cycles for the output to be switched on again after the output enable is asserted again. Is this correct? the SYNCN pin can also be used to mute the outputs. Is the behavior different?

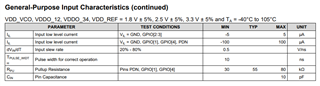

2: It is possible to continuously increase/decrease the frequency of the output clock with a frequency step defined in a register. GPIOs can be set as input for increasing/decreasing the frequency with predetermined steps, and a rising edge will toggle the increase/decrease with one step. What is the fastest frequency with which these rising edges can be sent to the CDCE6214 GPIOs?

BR,

Stefan