Other Parts Discussed in Thread: LMK04832

Hi team,

I want have two clocks with LMK04832EVM , one is 6.25M ,another is 16×6.25M 。and the two clocks have 90° phase difference.can you show me how to configure it. thanks.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi team,

I want have two clocks with LMK04832EVM , one is 6.25M ,another is 16×6.25M 。and the two clocks have 90° phase difference.can you show me how to configure it. thanks.

Hi Eric,

Just to clarify a few things:

1. By 16 x 6.25M, do you mean one 100MHz output or 16 additional 6.25 MHz outputs?

2. Which output frequency should used as the reference to measure a 90° phase difference? For example, is the 6.25MHz output leading by 90° or is it the other way around? A timing diagram would be helpful here to use as a reference.

3. Are you using the internal VCO or an external Clkin? A 90° phase shift is usually hard to implement just using the VCO frequencies. Do you mean 180°, or is it definitely 90°?

Once I have this information I can help set up a profile and test it out in the lab to make sure everything looks ok.

Regards,

Connor

Hi Connor,

1.the output is 100MHZ

2.the 6.25MHZ leading 90°

3.it is external CLK 200MHZ, it is definitely 90°

Hi Conner,

I also want to ask some question about the half step delay. the 2 cycle is standing for the sysref clock will be delayed for 2 clocks? and this delay refers to what clock? refer to itself or the other output clock?

Hi Conner, for the DDLYd2_EN,the minimum value can be set is 8, why i can turn down it to 4?and for the half delay. this cycle stand for a whole cycle of the output clock?

I think the best way is you can explain these configurations icons stand for what?

and you can show me how to set a certain output .Thanks

Hi Eric,

See the LMK04832 EVM User's Guide for some more information about the TICS Pro GUI for this device: https://www.ti.com/lit/ug/snau215a/snau215a.pdf

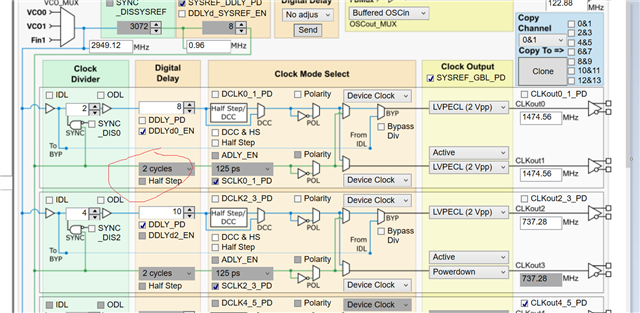

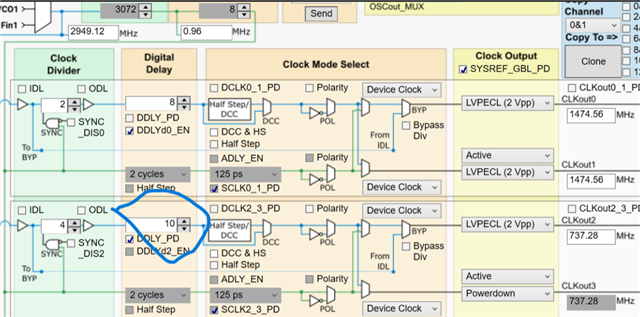

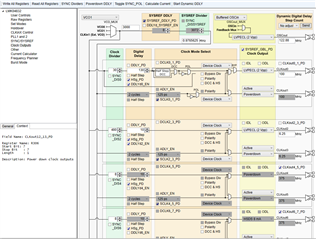

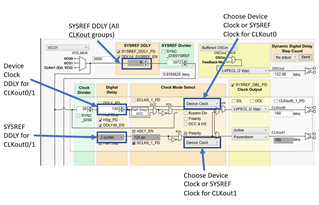

The DDLY code has a minimum value of 8 and a max value of 1023. The actual delay measurement equals the DDLY code multiplied by the period of the clock distribution frequency (seen at the top of the "Clock outputs" page).

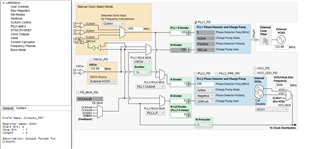

For this config I'll use a VCO1 frequency of 3000 MHz driven from CLKin1 = 200MHz and power down PLL1:

For a 90° phase shift at 6.25MHz, the delay between outputs should be 40 ns. Since delay = DDLY Code / Clock distribution frequency: DDLY Code = 40 ns * 3000 MHz = 120. So this means that there needs to be a difference of 120 in the DDLY code between 2 outputs to have a delay of 40 ns between them. I set the DDLY code for the 100 MHz output to be 130, and 10 for the 6.25 MHz output.

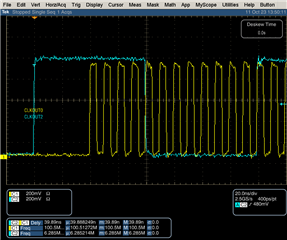

Note that I'm not using SYSREF for this config so I can power down the SYSREF block to reduce the power consumption, but you could use it if you wanted to use 1 clock output bank (like CLKout0/1 instead of CLKout0/2). You would just need to enable SYSREF, set the delay, and change the output clock mux from "Device Clock" to "SYSREF". Here's a quick measurement I took using this profile after syncing the outputs: :

:

CLKin1 200 MHz, VCO1 3000 MHz, CLKout0 100 MHz, CLKout2 6.25 MHz.tcs

I've attached the TICS Pro config as well, let me know if you have any other questions.

Regards,

Connor

Hi Conner,

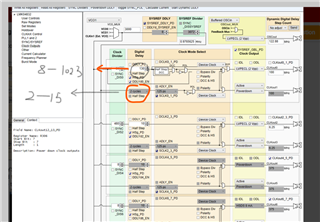

thanks for your reply, i have know how to set it and i want to know for the ch0 and ch1,the two have different delay configuration, can you tell why? for the ch0,it is delay can be set from 8-1023 but for the ch1,it only delay can only be 2-15 cycle.what the difference between them?

Hi Eric,

The DDLY code that ranges from 8-1023 is for both CLKout0 and CLKout1 if the device clock is selected. The 2nd box that ranges from 2-15 is for both CLKout0 and CLKout1 if the SYSREF clock is selected, and would be adding to the SYSREF delay at the top of the page. Essentially the device clock DDLY works independently from the SYSREF DDLY. Hopefully this picture makes things a little more clear

Regards,

Connor