Other Parts Discussed in Thread: DS25BR150,

Hi,

I have a number of very low jitter clocks coming offboard. I am looking for a buffer to restore the clocks in the 100MHz - 1GHz range with the lowest possible jitter.

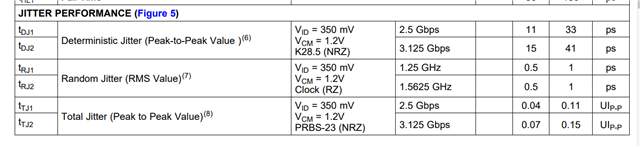

Is LMK1D2102 suitable for this? Initially I was planning to use DS25BR150 but I see this part has higher jitter?