Hello,

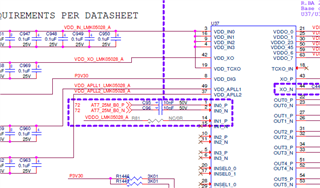

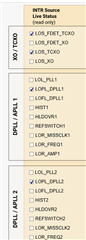

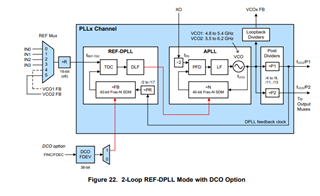

I have a design working with the LMK05028. I am attempting to use it in the 2 loop; REF, APLL mode.

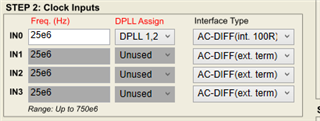

I have a LVDS input on IN0 at 25MHz and an XO at 48MHz. I'm using both PLL1 and 2 to output 100MHz and 312.5MHz respectively.

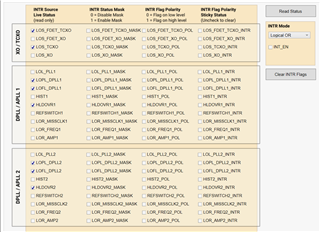

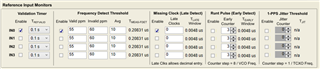

When I enable the frequency detect threshold, the PLL gets stuck in holdover mode regardless of the valid PPM settings.

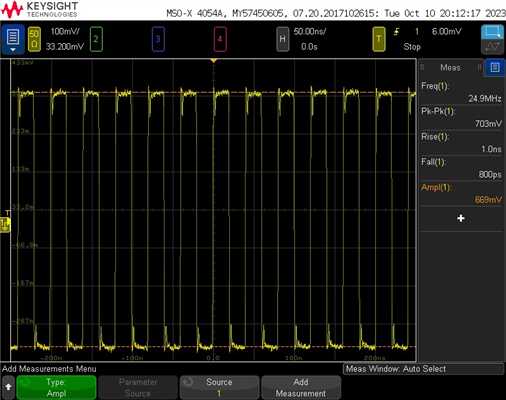

If I disable the frequency detect during the validation state, the PLL reports it is frequency locked but it never shows as phase locked.

When I probe the input and the output I can see there is no correlation between the phases.

Attached is the TCS file. Please let me know if I am missing something in the setup or if there is a way to debug the settings.

Thanks,

Ben Hirt