Hello TI team,

My customer use CDCE6214LTWRGETQ1 for their clock system. Could you pls help to review the schemetic.

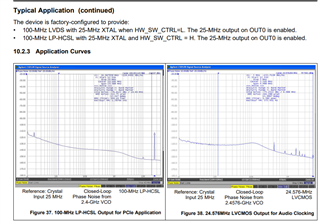

And their output devices are all 100MHZ. and they have some questions.

① If the Priref_p/n is not connected, will the output be affected?

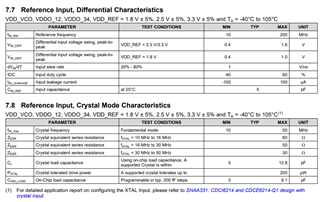

② At present, they use the two PINs of Secref_p/n to connect to the external crystal oscillator 25MHZ, can the output delivery a frequency of 100MHZ?

③ If they use the two PINs of Priref_p/n to connect to an external crystal oscillator 100MHZ, is it possible?