Hi Team,

May I know how to enable the LMK04832 one shot sysref mode? Thanks.

B.R.

Lucas

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Team,

May I know how to enable the LMK04832 one shot sysref mode? Thanks.

B.R.

Lucas

Hello Lucas,

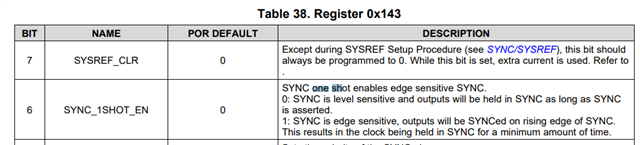

To enable one_shot all you have to do is set 0x143[6] = 1 as shown below on data sheet (p. 65).

Best,

Andrea

I noticed that the title asks about pulsed SYSREF mode, but the question asked about one shot SYSREF mode - these are two different things, and I want to make sure we answer your question in either case:

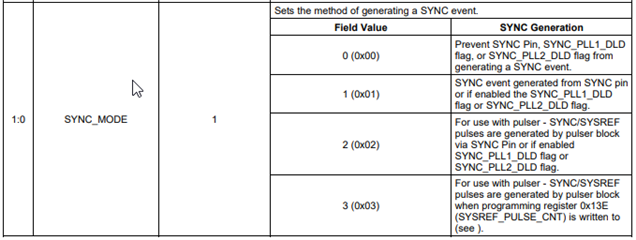

For the SYSREF pulser mode, the pulses are just a gated copy of the SYSREF divider. So the pulse duration and phase alignment relative to the device clocks will be the same as for continuous SYSREF. For example, if the SYSREF divider is programmed to produce 1MHz output, triggering the pulser will produce pulses with a period of 1MHz and a pulse width of 1 / (2 * 1 MHz). Since the pulser is just gating the SYSREF divider, the SYSREF divider needs to be synchronized to the clocks for proper alignment. Datasheet sections 8.3.4.1 and 8.3.5 offer guidance on how to ensure the SYSREF divider is aligned to the device clocks as desired.