Hi,

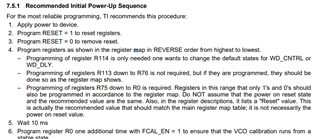

Concerning sub section "7.5.1 Recommended Initial Power-Up Sequence" from the datasheet.

1) For step 2. Program RESET=1 for register R0. Is then readback disabled when reset is asserted? We always readback zero's when reset is asserted.

For step 3. We readback the configuration of register R0 when reset is deasserted.

Therefore we assume that readback of register is disabled once reset is asserted. Is this assumption valid?

2) For step 4. Programming of registers.

Concerning the sentence "Programming of registers R113 down to R76 is not required, but if they are programmed, they should be done so as the register map shows".

Some of the registers in the aforementioned span are only readable (as e.g. R113). Therefore, why should we then program these registers when they are read only?

Can we program R114 and jump to register R75, and program all register down to R0, or does we violate with the recommend sequence of program the registers.

Best Regards,

Ole-Georg