Part Number: LMK04832

Other Parts Discussed in Thread: LMK5B33216

Hi Team,

Kindly help to review the approach, please suggest if we missed anything.

Target: We are using single PLL mode, and wish to synchronize the slave systems to the master system without any clock breakout.

Approach:

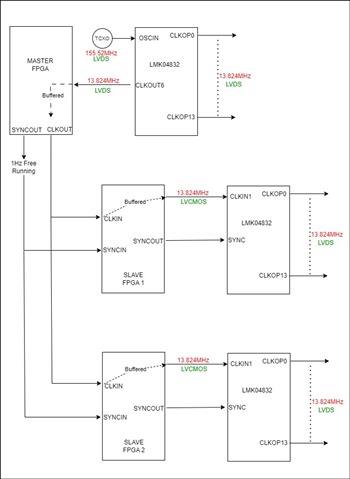

For the master device, the LMK04832 will generate the O/P clocks with the external TCXO (155.52MHz) connected to the OSCin Pin. Internal FB from CLKOUT6 is used for Cascaded 0-delay.

One of the clock outputs (13.824MHz) is fed back to the master FPGA. This clock and 1Hz Sync Pulse is transferred (buffered) from the master FPGA to the slave FPGAs.

Slave FPGA receives the clock (13.824Mhz) and uses this for the LMK Clock Input connected to the CLKIN1 pin. The slave FPGA synchronizes the SYNC OUT pulse with the SYNCIN which is fed to the LMK SYNC to synchronize the CLKOUTs with the master system.

The slave LMKs are synced with the master system once the power is on.