Hi,

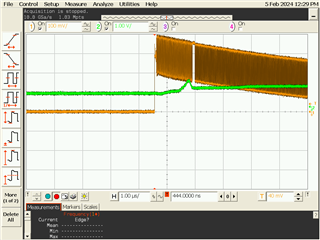

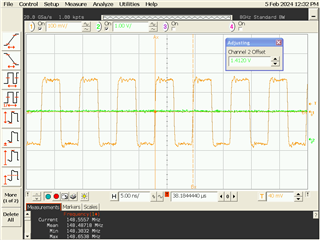

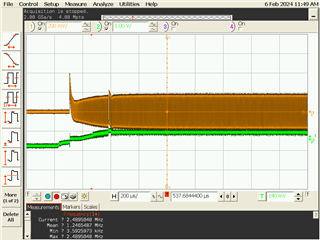

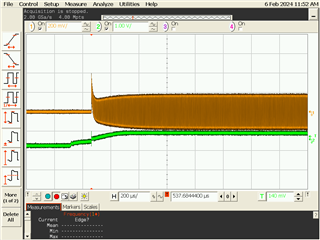

We are using CDCE62002 for Jitter cleaning.

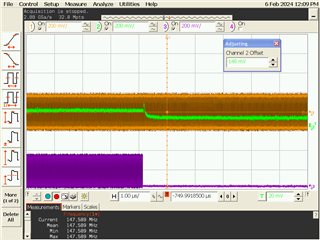

The device seems to have temperature Characteristics for lock time.

Because,

1. We input signal when the package is about 100℃, then CDCE62002 does not lock.

2. As the package temperature drops, CDCE62002 becomes lock state. The package is about 75.

Sometime the duration between 1 and 2 is a few minutes. The Reproducibility is high.

Do you have any information about this symptoms?

And we would like to know θJC. Only θJA is described in datasheet.

Thank you